From WikiChip

Difference between revisions of "apm/microarchitectures/storm"

(→Memory Hierarchy) |

|||

| Line 53: | Line 53: | ||

*** 64 B/line | *** 64 B/line | ||

*** Per chip | *** Per chip | ||

| + | |||

| + | == Die == | ||

| + | === Complete SoC === | ||

| + | * [[40 nm process]] | ||

| + | === Compute Complex === | ||

| + | * 4 PMDs | ||

| + | |||

| + | :[[File:apm storm potenza complex.png|700px]] | ||

| + | === Potenza processor module (PMD) === | ||

| + | * 2 cores per module | ||

| + | * shared L2 | ||

| + | * [[40 nm process]] | ||

| + | * 84,000,000 transistors | ||

| + | * 14.8 mm² die size | ||

| + | |||

| + | :[[File:apm storm module.png|700px]] | ||

| + | |||

| + | :[[File:apm storm module (annotated).png|700px]] | ||

== Bibliography == | == Bibliography == | ||

* Paramesh Gopi, Gaurav Singh, Greg Favor. ''"X-Gene: 64-bit ARM CPU and SoC."'' Hot Chips 24 Symposium (HCS), 2012 IEEE. IEEE, 2012. | * Paramesh Gopi, Gaurav Singh, Greg Favor. ''"X-Gene: 64-bit ARM CPU and SoC."'' Hot Chips 24 Symposium (HCS), 2012 IEEE. IEEE, 2012. | ||

| + | * Alfred Yeung, et al. (February, 2014). ''"A 3GHz 64b ARM v8 Processor in 40nm Bulk CMOS Technology"''. | ||

Revision as of 02:51, 26 September 2018

| Edit Values | |

| Storm µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | AppliedMicro |

| Manufacturer | TSMC |

| Introduction | 2011 |

| Process | 40 nm |

| Core Configs | 8 |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | ARMv8 |

| Succession | |

Storm is AppliedMicro first custom ARM microarchitecture for servers. Storm-based microprocessors were sold under the X-Gene 1 brand of server microprocessors.

Contents

Codenames

| Codename | Description |

|---|---|

| Potenza | codename for the core and memory sub-system |

Technology

Storm is fabricated on TSMC's 40 nm bluk CMOS.

Architecture

Memory Hierarchy

- Cache

- L1I

- 32 KiB, 8-way set associative

- Per core

- ECC and Parity protection

- 32 KiB, 8-way set associative

- L1D

- 32 KiB, 8-way set associative

- Per core

- 64 B/line

- Write-through with write-combining

- ECC and Parity protection

- 32 KiB, 8-way set associative

- L2

- 256 KB

- Per process module (2 cores)

- Inclusive of L1 write-thru data caches

- 64 B/line

- ECC and Parity protection

- 256 KB

- L3

- 8 MiB

- 64 B/line

- Per chip

- L1I

Die

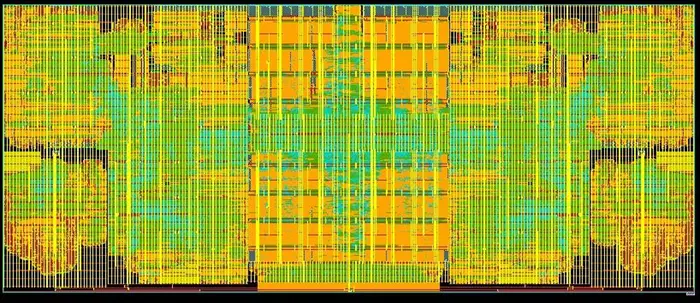

Complete SoC

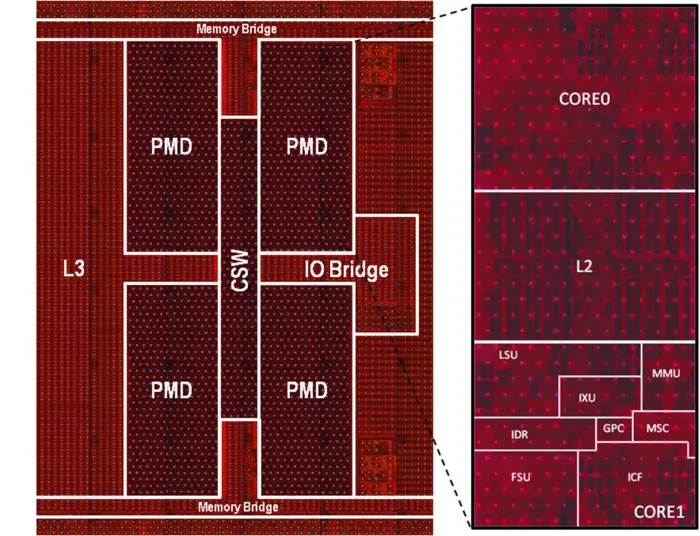

Compute Complex

- 4 PMDs

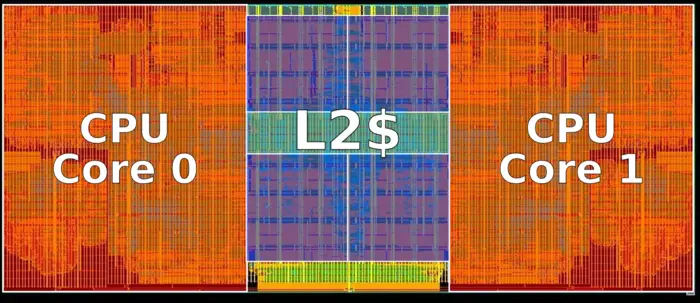

Potenza processor module (PMD)

- 2 cores per module

- shared L2

- 40 nm process

- 84,000,000 transistors

- 14.8 mm² die size

Bibliography

- Paramesh Gopi, Gaurav Singh, Greg Favor. "X-Gene: 64-bit ARM CPU and SoC." Hot Chips 24 Symposium (HCS), 2012 IEEE. IEEE, 2012.

- Alfred Yeung, et al. (February, 2014). "A 3GHz 64b ARM v8 Processor in 40nm Bulk CMOS Technology".

Facts about "Storm - Microarchitectures - AppliedMicro"

| codename | Storm + |

| core count | 8 + |

| designer | AppliedMicro + |

| first launched | 2011 + |

| full page name | apm/microarchitectures/storm + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Storm + |

| process | 40 nm (0.04 μm, 4.0e-5 mm) + |