| Edit Values | |

| Snapdragon 8cx | |

| |

| General Info | |

| Designer | Qualcomm, ARM Holdings |

| Manufacturer | TSMC |

| Model Number | 8cx |

| Market | Mobile |

| Introduction | December 6, 2018 (announced) Q3, 2019 (launched) |

| General Specs | |

| Family | Snapdragon 800 |

| Series | 800 |

| Locked | No |

| Frequency | 1,800 MHz, 2,840 MHz, 1,800 MHz, 3,020 MHz |

| Bus speed | 100 MHz |

| Clock multiplier | 28x |

| Microarchitecture | |

| ISA | ARMv8 (ARM) |

| Microarchitecture | Cortex-A76, Cortex-A55 |

| Core Name | Kryo 495 Gold, Kryo 495 Silver |

| Process | 7 nm |

| Technology | CMOS |

| Word Size | 64 bit |

| Cores | 8 |

| Threads | 8 |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| Vcore | 0.5 V-0.95 V |

| TDP | 7 W |

| Packaging | |

| |

| Succession | |

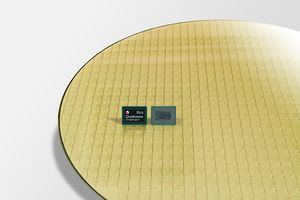

Snapdragon 8cx (Snapdragon 8 Compute eXtreme) is a high-performance 64-bit ARM LTE system on a chip designed by Qualcomm and introduced in late 2018. Fabricated on TSMC's 7nm process, the 8cx features four Kryo 495 Silver high-efficiency cores operating at 1.8 GHz along with four high-performance Kryo 495 Gold operating at 2.84 GHz. The Snapdragon 8cx integrates the Adreno 680 GPU operation at ? MHz and features an X24 LTE modem supporting Cat 20 uplink and Cat 20 downlink. This chip supports up to ? GiB of octa-channel LPDDR4X-4266 memory.

Contents

Overview

The Snapdragon 8cx was announced by Qualcomm on December 6, 2018. The chip is what Qualcomm considers a new high tier Snapdragon aimed at always-connected PCs with higher performance and thermal headroom over traditional smartphone devices. The chip comprise of a quad-core cluster of Kryo 495 Gold (Cortex-A76) big cores and a quad-core cluster of Kryo 495 Silver (Cortex-A55) little cores.

Cache

- Main articles: Cortex-A76 § Cache and Cortex-A55

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

||||||||

|

||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||||||

|

||||||||||||||||||

- SSD: NVME SSD

- UFS: UFS 3.0

DSP

This chip features Qualcomm's Hexagon 685 DSP.

Graphics

|

Integrated Graphics Information

|

||||||||||||||||||||||||||

|

||||||||||||||||||||||||||

- Codec Support: H.265 (HEVC), H.264 (AVC), VP9

- Playback: Up 4K HDR decode at 120fps

- Capture:

- 4K Video Capture for Ultra HD Premium Displays (4K@30fps)

- Slow Motion video capture (720p@480fps)

Camera

- ISP

- Dual 14-bit ISPs

- Qualcomm Spectra 390 image signal processor

- Up to 16 MP dual camera

- Up to 32 MP single camera

Connectivity

- X24 LTE modem

- LTE Category 20

- Downlink:

- 2 Gbps peak

- 7x20 MHz carrier aggregation

- Up to 256-QAM

- Up to 4x4 MIMO on five carriers

- Full-Dimension MIMO (FD-MIMO)

- Maximum 20 spatial streams

- Uplink:

- 316 Mbps peak

- 3x20 MHz carrier aggregation

- Up to 2x 106Mbps LTE streams

- Up to 256-QAM

- Uplink data compression

- LTE FDD, LTE TDD including CBRS support, LAA, LTE Broadcast, WCDMA (DB-DC-HSDPA, DC-HSUPA), TD-SCDMA, CDMA 1x, EV-DO, GSM/EDGE

- WiFi

- Standards: 802.11ad, 802.11ac Wave 2, 802.11a/b/g, 802.11n

- Spectral Bands: 2.4 GHz, 5 GHz, 60 GHz

- MIMO Configuration: 2x2 (2-stream)

- Bluetooth

- Bluetooth 5.0

Location

- Systems: GPS, GLONASS, Beidou, Galileo, QZSS, SBAS

Utilizing devices

- Galaxy Book S

Documents

- all microprocessor models

- microprocessor models by qualcomm

- microprocessor models by qualcomm based on cortex-a76

- microprocessor models by qualcomm based on cortex-a55

- microprocessor models by arm holdings

- microprocessor models by arm holdings based on cortex-a76

- microprocessor models by arm holdings based on cortex-a55

- microprocessor models by tsmc

- future microprocessor models

| back image |  + + |

| base frequency | 1,800 MHz (1.8 GHz, 1,800,000 kHz) +, 2,840 MHz (2.84 GHz, 2,840,000 kHz) + and 3,020 MHz (3.02 GHz, 3,020,000 kHz) + |

| bus speed | 100 MHz (0.1 GHz, 100,000 kHz) + |

| core count | 8 + |

| core name | Kryo 495 Gold + and Kryo 495 Silver + |

| core voltage (max) | 0.95 V (9.5 dV, 95 cV, 950 mV) + |

| core voltage (min) | 0.5 V (5 dV, 50 cV, 500 mV) + |

| designer | Qualcomm + and ARM Holdings + |

| dsp | Hexagon 685 DSP + |

| family | Snapdragon 800 + |

| first announced | December 6, 2018 + |

| first launched | March 2019 + |

| full page name | qualcomm/snapdragon 800/8cx + |

| has ecc memory support | false + |

| has locked clock multiplier | false + |

| instance of | microprocessor + |

| integrated gpu | Adreno 680 GPU + |

| integrated gpu designer | Qualcomm + |

| isa | ARMv8 + |

| isa family | ARM + |

| l3$ size | 10 MiB (10,240 KiB, 10,485,760 B, 0.00977 GiB) + |

| ldate | 3000 + |

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Mobile + |

| max cpu count | 1 + |

| max memory bandwidth | 63.58 GiB/s (65,105.92 MiB/s, 68.269 GB/s, 68,268.505 MB/s, 0.0621 TiB/s, 0.0683 TB/s) + |

| max memory channels | 8 + |

| microarchitecture | Cortex-A76 + and Cortex-A55 + |

| model number | 8cx + |

| name | Snapdragon 8cx + |

| process | 7 nm (0.007 μm, 7.0e-6 mm) + |

| series | 800 + |

| smp max ways | 1 + |

| supported memory type | LPDDR4X-4266 + |

| tdp | 7 W (7,000 mW, 0.00939 hp, 0.007 kW) + |

| technology | CMOS + |

| thread count | 8 + |

| used by | Galaxy Book S + |

| word size | 64 bit (8 octets, 16 nibbles) + |