| Edit Values | |

| 7 Series µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | SiFive |

| Manufacturer | TSMC, GlobalFoundries |

| Introduction | October 21, 2018 |

| Core Configs | 1, 2, 4, 6, 8 |

| Pipeline | |

| Type | Superscalar, Pipelined |

| OoOE | No |

| Speculative | Yes |

| Reg Renaming | No |

| Stages | 8 |

| Decode | 2 |

| Instructions | |

| ISA | RISC-V |

| Cores | |

| Core Names | E76, E76-MC, S76, S76-MC, U74, U74-MC |

| Succession | |

7 Series is a series of high-performance RISC-V IP cores designed by SiFive.

Contents

Architecture

Key changes from 5 Series

- Core

- 8-stage pipeline (from 5-7)

- 10% higher frequency

- dual-issue

- Memory subsystem

- 0-cycle load-to-use latency (down from 1 cycle)

- 2-cycle SRAM access time worst case (down from 5 cycles)

- Fast I/O Port (FIO Port)

- 8-stage pipeline (from 5-7)

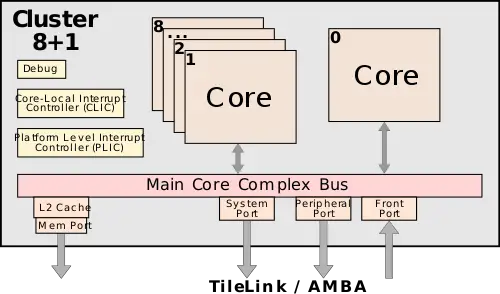

Block Diagram

Cluster

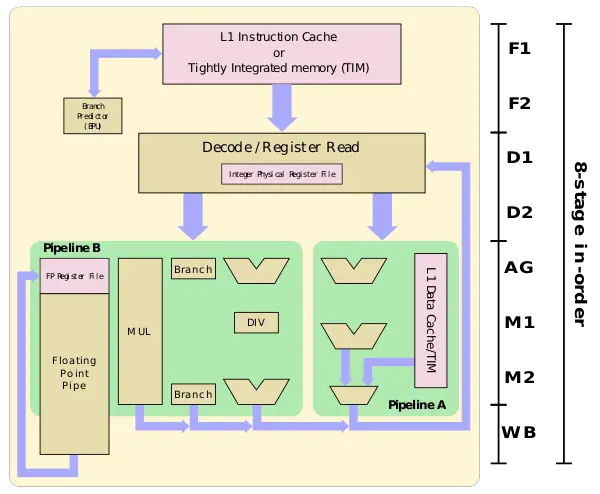

Core

Overview

The 7 Series is based on an improved version of the 5 Series which SiFive claims to provide 60% improvement in CoreMarks/MHz as well as 40% improvement in DMIPS/MHz. Series 7 base design is a cluster of up to 9 cores (8+1). Cores can be a mix of 7 Series cores as well as SiFive other existing cores. Everything in the cluster is cache coherent - including any extended SRAM options as well as any custom accelerator attached to the cores. The cluster can be further scaled up through the use of AMBA or TileLink which allows for up to 64 clusters to be integrated onto a single chip. Multi-chip support is also possible via ChipLink.

Core

7 Series cores are based on a dual-issue in-order pipelined design.

Cluster

The basic cluster comprises up to 9 cores configured as 8+1. The type of cores is fully customizable and may incorporate SiFive previous cores (e.g. the high-efficiency 2 Series cores). All the cores sit on a cache coherent bus.

Cores

| Core | Perf | Comperable | ISA |

|---|---|---|---|

| E7 | 2.3 DMIPS/MHz 4.9 CoreMarks/MHz |

Cortex-M7 | RV32GCV |

| S7 | 2.5 DMIPS/MHz 4.9 CoreMarks/MHz |

Cortex-R8 | RV64GCV |

| U7 | 2.5 DMIPS/MHz 4.9 CoreMarks/MHz |

Cortex-A55 | RV64GCV |

| codename | 7 Series + |

| core count | 1 +, 2 +, 4 +, 6 + and 8 + |

| designer | SiFive + |

| first launched | October 21, 2018 + |

| full page name | sifive/microarchitectures/7 series + |

| instance of | microarchitecture + |

| instruction set architecture | RISC-V + |

| manufacturer | TSMC + and GlobalFoundries + |

| microarchitecture type | CPU + |

| name | 7 Series + |

| pipeline stages | 8 + |