| Edit Values | |

| A12 Bionic | |

| General Info | |

| Designer | Apple |

| Manufacturer | TSMC |

| Model Number | A12 Bionic |

| Market | Mobile, Embedded |

| Introduction | September 12, 2018 (announced) September 21, 2018 (launched) |

| General Specs | |

| Family | Ax |

| Frequency | 2,400 MHz |

| Microarchitecture | |

| ISA | ARMv8.3 (ARM) |

| Microarchitecture | Vortex, Tempest |

| Core Name | Vortex, Tempest |

| Process | 7 nm |

| Transistors | 6,900,000,000 |

| Technology | CMOS |

| Die | 83.27 mm² 9.89 mm × 8.42 mm |

| Word Size | 64 bit |

| Cores | 6 |

| Threads | 6 |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Succession | |

A12 Bionic is a 64-bit hexa-core ARM performance mobile system on a chip introduced by Apple in late 2018 as a successor to the A11.

Overview

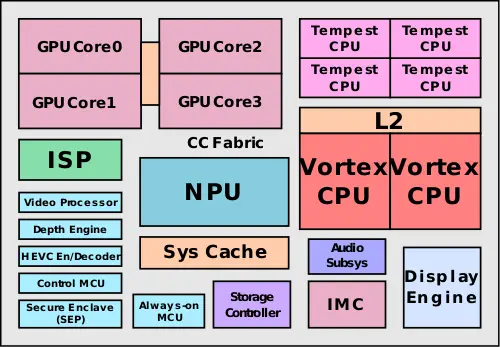

Fabricated on TSMC 7 nm process and integrating 6.9 billion transistors, the A12 features two big Vortex cores operating at up to 2.4 GHz along with four little Tempest high-efficiency cores. Apple claims the big cores are up to 15% faster than the one in the A11 while being up to 40% more efficient. For the four high-efficiency cores, Apple claims up to 50% higher efficiency. Note that all six cores can operate concurrently.

The A12 features an Apple-designed graphics processor that is said to deliver up to 50% higher performance as well as a neural processor capable of peak performance of 5 TOPS (int8).

ISP

The A12 incorporates Apple's image signal processor (ISP), codename Petra, for camera related applications. The ISP is said to deliver faster depth engine and an improved video processor.

Integrated Graphics

The A12 incorporates an Apple-designed GPU. The GPU is a four-core design which is said to deliver 50% performance over the A11 in tessellation and multi-layer rendering as well as lossless memory compression.

Neural Engine

The A12 chip features an improved neural engine, codename Quin. Apple stated this is an 8-core design (the A11 featured what they called a dual-core design). The new engine is capable of performing real-time processing at 5 trillion 8-bit operations per second (up from 600 billion).

Utilizing devices

- iPhone XR

- iPhone XS

- iPhone XS Max

This list is incomplete; you can help by expanding it.

Bibliography

- Apple Keynote. (September 12, 2018). Apple Special Event.

- Daniel Yang, Stacy Wegner. (September 17, 2018) "Apple iPhone Xs Max Teardown". TechInsights.

| base frequency | 2,400 MHz (2.4 GHz, 2,400,000 kHz) + |

| core count | 6 + |

| core name | Vortex + and Tempest + |

| designer | Apple + |

| die area | 83.27 mm² (0.129 in², 0.833 cm², 83,270,000 µm²) + |

| die length | 9.89 mm (0.989 cm, 0.389 in, 9,890 µm) + |

| die width | 8.42 mm (0.842 cm, 0.331 in, 8,420 µm) + |

| family | Ax + |

| first announced | September 12, 2018 + |

| first launched | September 21, 2018 + |

| full page name | apple/ax/a12 + |

| instance of | microprocessor + |

| isa | ARMv8.3 + |

| isa family | ARM + |

| ldate | September 21, 2018 + |

| manufacturer | TSMC + |

| market segment | Mobile + and Embedded + |

| max cpu count | 1 + |

| microarchitecture | Vortex + and Tempest + |

| model number | A12 Bionic + |

| name | A12 Bionic + |

| process | 7 nm (0.007 μm, 7.0e-6 mm) + |

| smp max ways | 1 + |

| technology | CMOS + |

| thread count | 6 + |

| transistor count | 6,900,000,000 + |

| used by | iPhone XR +, iPhone XS + and iPhone XS Max + |

| word size | 64 bit (8 octets, 16 nibbles) + |