From WikiChip

SABRE - Intel Movidius

| Edit Values | |

| SABRE | |

| General Info | |

| Designer | Movidius |

| Manufacturer | TSMC |

| Model Number | SABRE |

| Market | Embedded, Mobile |

| General Specs | |

| Frequency | 180 MHz |

| Microarchitecture | |

| ISA | SPARC V8 (SPARC), SHAVE (SHAVE) |

| Microarchitecture | LEON3, SHAVE v2.0 |

| Process | 65 nm |

| Technology | CMOS |

| Word Size | 32 bit |

| Cores | 9 |

| Threads | 9 |

SABRE was a test microprocessor designed by Movidius for the acceleration of machine vision. SABRE was a modification of the original ISAAC designed back in 2007 as a game physics accelerator. The SABRE microprocessor eventually lead to the production definition of the Myriad 1 line of vision accelerators.

Overview[edit]

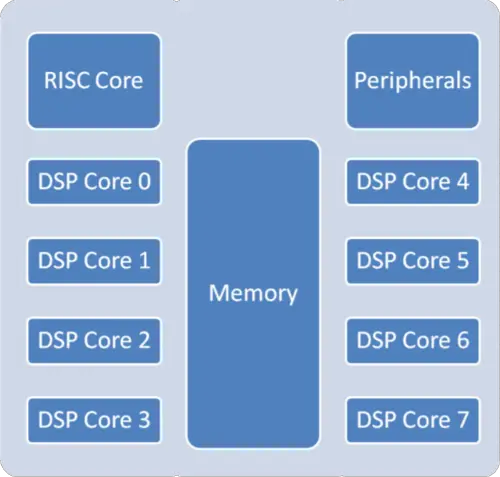

SABRE is capable of 20 GLOPS at low 100s mW of power through the use of 9 execution units consisting of a SPARC V8 LEON3 core and 8 additional SHAVE v2.0 cores.

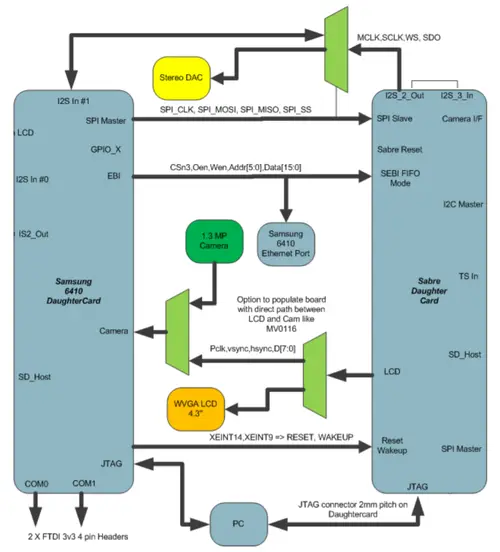

The test platform consisted of a Samsung 6410 daughtercard which incoluded an S3C6410X processor (ARM11) and a Movidius MV0108 SABRE daughtercard which had the SABRE processor.

Block diagram[edit]

References[edit]

- Tite, Teodor, et al. "moviOS: a Real-Time Multiprocessor Operating System for Multimedia Applications."

- Happy 10th Birthday Movidius

Facts about "SABRE - Intel Movidius"

| base frequency | 180 MHz (0.18 GHz, 180,000 kHz) + |

| core count | 9 + |

| designer | Movidius + |

| full page name | movidius/sabre + |

| instance of | microprocessor + |

| isa | SPARC V8 + and SHAVE + |

| isa family | SPARC + and SHAVE + |

| ldate | 1900 + |

| manufacturer | TSMC + |

| market segment | Embedded + and Mobile + |

| microarchitecture | LEON3 + and SHAVE v2.0 + |

| model number | SABRE + |

| name | SABRE + |

| process | 65 nm (0.065 μm, 6.5e-5 mm) + |

| technology | CMOS + |

| thread count | 9 + |

| word size | 32 bit (4 octets, 8 nibbles) + |