-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

ISAAC - Intel Movidius

< movidius

| Edit Values | |

| ISAAC | |

| |

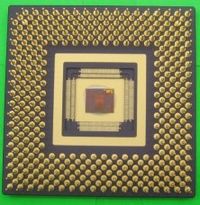

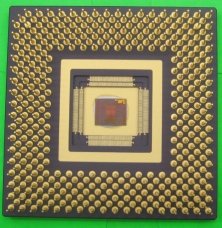

| ISAAC test chip | |

| General Info | |

| Designer | Movidius |

| Manufacturer | TSMC |

| Model Number | Movidius |

| Market | Embedded, Mobile |

| Introduction | 2007 (announced) |

| Microarchitecture | |

| Process | 65 nm |

| Technology | CMOS |

ISAAC was an initial test microprocessor designed by Movidius (then Movidia) for accelerating game-physics. Manufactured on TSMC's 65 nm process, that chip taped out in late 2007 with silicon back in early 2008. After various discussions with phone manufacturers it was determined that a discrete game physics chip for mobile phones was too expensive, however the acceleration of vision processing was needed. The ISAAC was eventually reworked as the SEBRE which included acceleration for vision processing which eventually became the Myriad 1 family.

References

Retrieved from "https://en.wikichip.org/w/index.php?title=movidius/isaac&oldid=75089"

Facts about "ISAAC - Intel Movidius"

| designer | Movidius + |

| first announced | 2007 + |

| full page name | movidius/isaac + |

| instance of | microprocessor + |

| ldate | 2007 + |

| main image |  + + |

| main image caption | ISAAC test chip + |

| manufacturer | TSMC + |

| market segment | Embedded + and Mobile + |

| model number | Movidius + |

| name | ISAAC + |

| process | 65 nm (0.065 μm, 6.5e-5 mm) + |

| technology | CMOS + |