| Edit Values | ||||||

| GAP8 | ||||||

| ||||||

| GAP8, front package | ||||||

| General Info | ||||||

| Designer | GreenWaves | |||||

| Manufacturer | TSMC | |||||

| Model Number | GAP8 | |||||

| Market | Embedded | |||||

| Introduction | October, 2016 (announced) February 26, 2018 (launched) | |||||

| Release Price | $5 | |||||

| General Specs | ||||||

| Frequency | 250 MHz | |||||

| Microarchitecture | ||||||

| ISA | RV32IMC (RISC-V) | |||||

| Process | 55 nm | |||||

| Technology | CMOS | |||||

| Word Size | 32 bit | |||||

| Cores | 9 | |||||

| Threads | 9 | |||||

| Multiprocessing | ||||||

| Max SMP | 1-Way (Uniprocessor) | |||||

| Electrical | ||||||

| Power dissipation | 60 mW | |||||

| Vcore | 1 V-1.2 V | |||||

| VI/O | 1.8 V, 3.3 V | |||||

| Packaging | ||||||

| ||||||

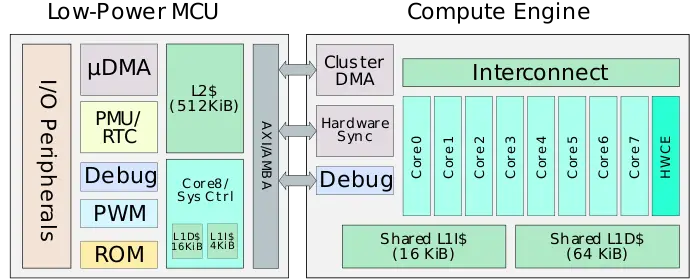

GAP8 is a nona-core 32-bit RISC-V ultra-low power microprocessor designed by GreenWaves and introduced in early 2018 for the edge computing and IoT market. This processor, which is fabricated on TSMC's 55LP process, is based on the PULP open core. The GAP8 incorporates nine RISC-V cores along with a neural process designed to accelerate convolutional neural networks (CNN). The GAP8 is said to offer a peak performance of up to 200 MOPS at 1 mW and up to 10 GOPS at a few tens of mW, making it well suitable for long autonomous battery-powered life.

Overview

Cache

The GAP8 a private L1 cache for the MCU core which consists of a 16 KiB of data cache and 4 KiB of instruction cache. The compute engine has a shared level 1 cache of its own which consists of a 16 KiB instruction cache and a 64 KiB data cache. Additional, the entire chip shares a 512 KiB level 2 cache consisting of 4 128 KiB cache banks.

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory

The chip supports up to 16 MiB of SDRAM or additional RAM through the HyperBus interface.

Expansions

- 128 Mb/s LVDS IEEE compliant

- Serial I/Q

- UART

- Quad SPI Master + additional SPI Master

- SPI Slave

- I2S (2)

- I2C (2)

- Camera parallel interface (CPI)

- HyperBus (External Flash and RAM)

- 32 x GPIOs

Features

- 4x PWM

- 32 kHz external quartz

- Programmable Voltage Regulator

- Real Time Clock

- 2 programmable clocks

- Secured execution support with Memory Protection Unit (MPU)

See also

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | GAP8 - GreenWaves#package + |

| base frequency | 250 MHz (0.25 GHz, 250,000 kHz) + |

| core count | 9 + |

| core voltage (max) | 1.2 V (12 dV, 120 cV, 1,200 mV) + |

| core voltage (min) | 1 V (10 dV, 100 cV, 1,000 mV) + |

| designer | GreenWaves + |

| first announced | October 2016 + |

| first launched | February 26, 2018 + |

| full page name | greenwaves/gap8 + |

| instance of | microprocessor + |

| io voltage | 1.8 V (18 dV, 180 cV, 1,800 mV) + and 3.3 V (33 dV, 330 cV, 3,300 mV) + |

| isa | RV32IMC + |

| isa family | RISC-V + |

| l1$ size | 100 KiB (102,400 B, 0.0977 MiB) + |

| l1d$ size | 80 KiB (81,920 B, 0.0781 MiB) + |

| l1i$ size | 20 KiB (20,480 B, 0.0195 MiB) + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| ldate | February 26, 2018 + |

| main image |  + + |

| main image caption | GAP8, front package + |

| manufacturer | TSMC + |

| market segment | Embedded + |

| max cpu count | 1 + |

| model number | GAP8 + |

| name | GAP8 + |

| package | aQFN + |

| power dissipation | 0.06 W (60 mW, 8.046e-5 hp, 6.0e-5 kW) + |

| process | 55 nm (0.055 μm, 5.5e-5 mm) + |

| release price | $ 5.00 (€ 4.50, £ 4.05, ¥ 516.65) + |

| smp max ways | 1 + |

| technology | CMOS + |

| thread count | 9 + |

| word size | 32 bit (4 octets, 8 nibbles) + |