| Edit Values | |

| Socket G34 | |

| General Info | |

| Designer | AMD |

| Introduction | March 29, 2010 (launched) |

| Market | Server |

| Microarchitecture | K10, Bulldozer, Piledriver |

| TDP | 140 W 140,000 mW 0.188 hp 0.14 kW |

| Package | |

| Name | LGA-1944 |

| Type | Organic Flip-Chip Land Grid Array |

| Contacts | 1944 |

| Dimension | 42.5 mm 4.25 cm × 60.0 mm1.673 in 6 cm 2.362 in |

| Pitch | 1.00 mm 0.0394 in |

| Socket | |

| Name | Socket G34 |

| Type | LGA |

Socket G34 was designed for LGA-1944-packaged AMD Opteron 6000 Series microprocessors optimized for performance per Watt and scalability. The designation G34 stands for AMD's third generation server socket with four memory channels. Socket G34 has a DDR3 memory interface while its predecessors Socket 940 and Socket F were designed for DDR and DDR2 memory, respectively, and also offers additional HyperTransport links to improve the bandwidth and latency between nodes on multiprocessor systems. It has a smaller sibling Socket C32 which supports two memory channels and three HT links as the prior generations. Uniprocessor Opterons with a DDR3 interface were released in packages for Socket AM3 and AM3+ which make a single HT link available. Socket G34 was superseded by Socket SP3.

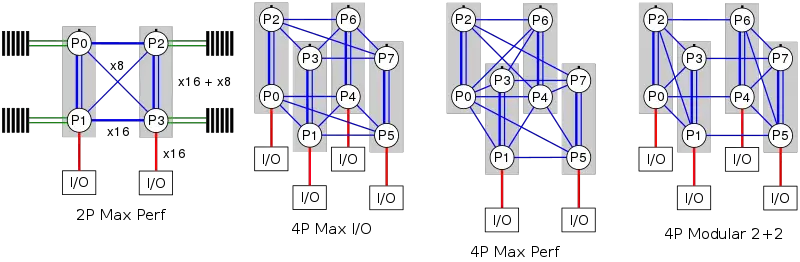

The LGA-1944 package is a multi-chip module integrating two dies, each providing four 16-bit HyperTransport Gen 3 links and two DDR3 memory controllers. Each HT link can be further unganged into two independent 8-bit links. The package has 1132 signal I/O, 341 power, and 471 ground pins. Package size constrained the HT interface to 64 lanes total, one x16 and one x8 link from node 0, two x16 links and one x8 link from node 1. One x16 link on node 0 is not connected, the remaining links connect the nodes in the package. Each link can be used for I/O, e.g. connecting a GPU through a HT-PCI bridge, or for cache coherent inter-socket traffic using an AMD proprietary protocol, with flexible routing permitting various network topologies on 2P and 4P systems. 8P systems were not considered citing insufficient demand.

Socket G34 was used in AMD's 2- and 4-socket "Maranello" reference platform. The processors for this socket are members of AMD's Family 10h with up to 12 CPU cores based on the K10 microarchitecture, and Family 15h featuring up to 8 compute units (not exactly 16 cores) based on the Bulldozer and Piledriver microarchitectures. They were fabricated on 45 nm and 32 nm processes.

Supposedly AMD originally planned a 1305-pin "Socket G3" for 1P to 8P systems with two DDR3 memory channels per socket. To reach higher memory capacities AMD proposed a "G3 Memory Extender" (G3MX) chip mounted on the motherboard to buffer the signals of four RDIMMs on two channels, and up to two G3MXs connected to each CPU memory channel.

Contents

Features

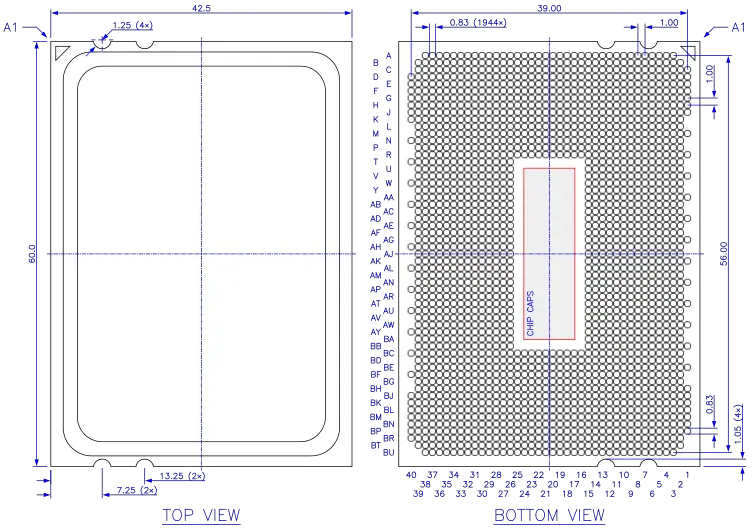

- 1944-land lidded land grid array package, 42.5 × 60.0 mm, 40 × 57 land array, 1.0 mm pitch, organic substrate, C4 (flip chip) die attachment

- 4 × 64/72 bit DDR3 SDRAM interface up to 933 MHz, PC3-14900 (DDR3-1866), 29.9 GB/s

- Up to 12 SR/DR/QR RDIMMs, 12 SR/DR LRDIMMs (Fam. 15h), or 8 SR/DR UDIMMs

- JEDEC 1.5V, 1.35V, 1.25V (Fam. 15h)

- SEC-DED ECC support

- AMD Memory Controller PowerCap (Fam. 15h)

- On-line spare feature provides single-rank DRAM redundancy

- 3 × 16 + 2 × 8 bit HyperTransport 1.0/3.0 interface up to 3200 MHz, 6400 MT/s, 12.8 GB/s in each direction

- HT Assist Technology (probe filter)

- Link Speed PowerCap (Fam. 15h)

- Link Width PowerCap (Fam. 15h)

- Managemement Features

- Advanced Platform Management Link (APML)

- SMBus v2.0-compatible interface

- Remote-Management Interface (SB-RMI)

- Power Management

- Multiple low-power states

- Independent Dynamic Core Technology (Fam. 10h)

- AMD CoolCore Technology (Fam. 10h)

- Dual Dynamic Power Management (Fam. 10h)

- Advanced Power Management (Fam. 15h)

- AMD Turbo CORE technology with per core power gating (Fam. 15h)

- CPU PowerCap (Fam. 15h)

- Effective frequency interface (Fam. 15h)

- ACPI-compliant

- Supported power states Fam. 10h: C0, C1, C1E, S0, S1, S3, S4, S5

- Supported power states Fam. 15h: C0, C1, C1E, C6, CC6, S0, S3, S4, S5

- Hardware thermal control

Chipsets

- AMD SR5690, SR5670, SR5650

- AMD SP5100 southbridge

Processors using Socket G34

- Opteron 6100 "Magny Cours"

- Opteron 6200 "Interlagos"

- Opteron 6300 "Abu Dhabi", "Warsaw"

- Embedded Opteron (same silicon as "Magny Cours")

| List of all Socket G34-based Processors | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Model | Price | Process | Launched | µarch | Family | Core | C | T | Freq | Turbo | TDP | ||||||||

| Count: 0 | |||||||||||||||||||

Package Diagram

LGA-1944 package. All dimensions in millimeters.

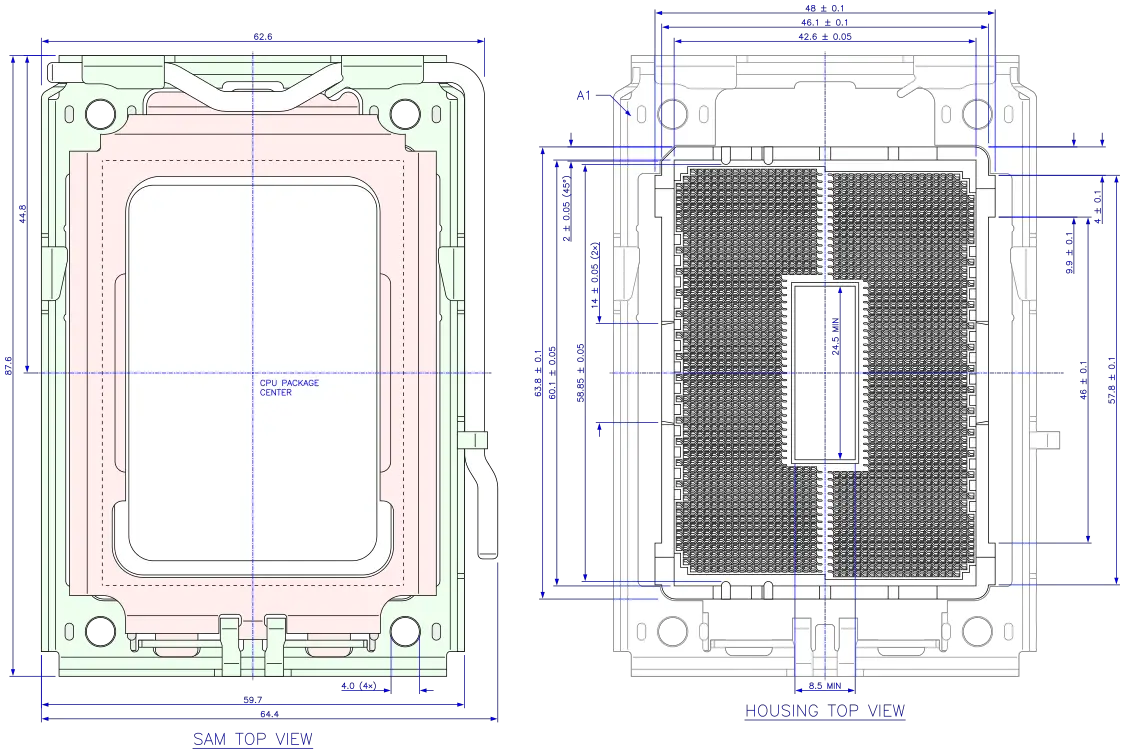

Socket Diagram

Dimensions of TE Connectivity LGA Socket 1944 (G34), Part No. 2069189. All dimensions in millimeters.

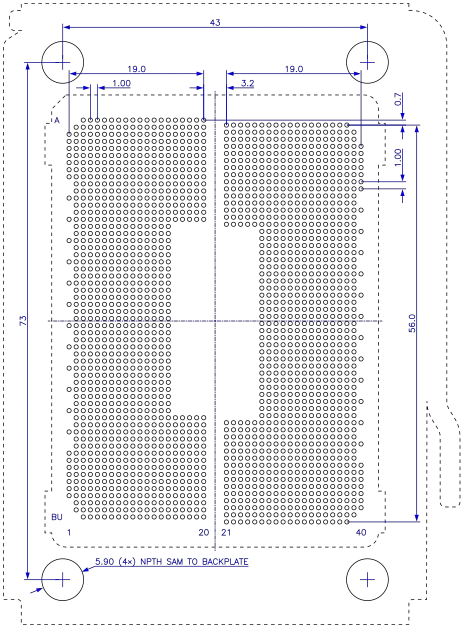

PCB layout of TE Connectivity Socket G34. All dimensions in millimeters.

Pin Map

No data available.

References

- "Family 10h AMD Opteron Processor Product Data Sheet", AMD Publ. #40036, Rev. 3.04, June 22, 2010

- "Family 15h Models 00h-0Fh AMD Opteron Processor Product Data Sheet", AMD Publ. #49687, Rev. 3.01, October 10, 2012

- "BIOS and Kernel Developer’s Guide (BKDG) For AMD Family 10h Processors", AMD Publ. #31116, Rev. 3.62, January 14, 2013

- "BIOS and Kernel Developer’s Guide (BKDG) for AMD Family 15h Models 00h-0Fh Processors", AMD Publ. #42301, Rev. 3.14, January 28, 2013

- "Revision Guide for AMD Family 10h Processors", AMD Publ. #41322, Rev. 3.92, March 2012

- "Revision Guide for AMD Family 15h Models 00h-0Fh Processors", AMD Publ. #48063, Rev. 3.24, September 30, 2014

- Conway, Pat; Kalyanasundharam, Nathan; Donley, Gregg; Lepak, Kevin; Hughes, Bill (2010). Cache Hierarchy and Memory Subsystem of the AMD Opteron Processor. IEEE Micro. 30 (2): 16-29. doi:10.1109/MM.2010.31

- Financial Analyst Day Presentation, November 11, 2009

See also

| designer | AMD + |

| first launched | March 29, 2010 + |

| instance of | package + |

| market segment | Server + |

| microarchitecture | K10 +, Bulldozer + and Piledriver + |

| name | Socket G34 + |

| package | LGA-1944 + |

| package contacts | 1,944 + |

| package length | 60 mm (6 cm, 2.362 in) + |

| package pitch | 1 mm (0.0394 in) + |

| package type | FC-OLGA + |

| package width | 42.5 mm (4.25 cm, 1.673 in) + |

| socket | Socket G34 + |

| tdp | 140 W (140,000 mW, 0.188 hp, 0.14 kW) + |