From WikiChip

Socket TR4 (sTR4) - Packages - AMD

| Edit Values | |

| Socket TR4 | |

| General Info | |

| Designer | AMD |

| Introduction | May 16, 2017 (announced) August 10, 2017 (launched) |

| Market | Desktop |

| Microarchitecture | Zen, Zen+ |

| TDP | 180 W 180,000 mW , 250 W0.241 hp 0.18 kW 250,000 mW 0.335 hp 0.25 kW |

| Package | |

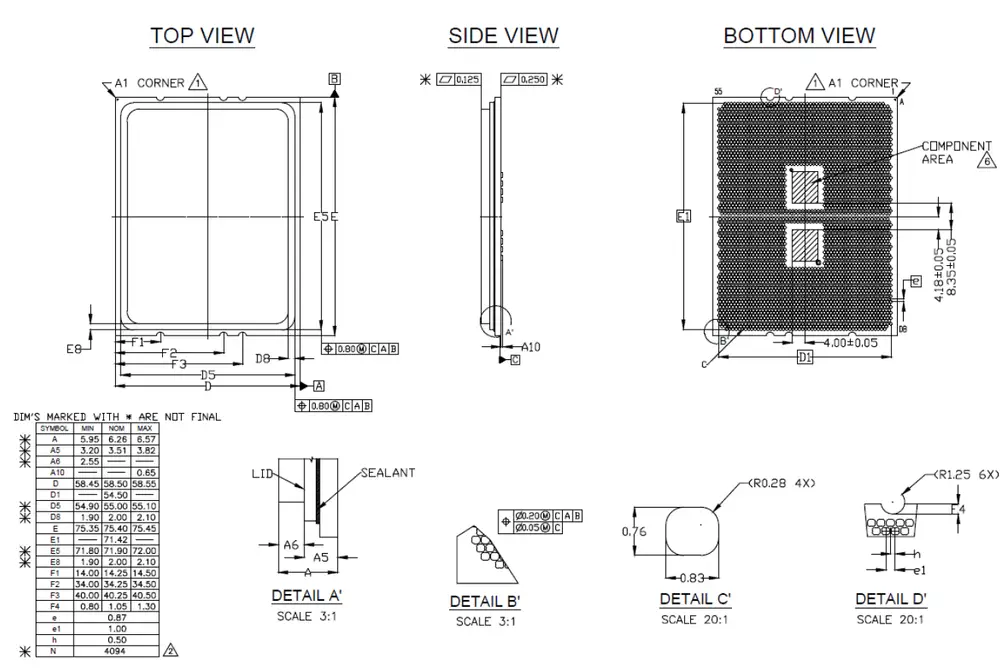

| Name | FCLGA-4094 |

| Type | Organic Flip-Chip Land Grid Array |

| Contacts | 4094 |

| Dimension | 58.5 mm 5.85 cm × 75.4 mm2.303 in 7.54 cm 2.969 in |

| Pitch | 1.00 mm 0.0394 in |

| Socket | |

| Name | Socket TR4, sTR4, Socket SP3r2 |

| Type | LGA |

Socket TR4 (sTR4) also Socket SP3r2 is a land grid array microprocessor socket designed by AMD for their Threadripper family supported by the Zen and Zen+ microarchitectures. This socket is designed for ICs with a 4094-contact FCLGA packages.

Contents

Overview

sTR4 is a socket specifically designed by AMD for their Threadripper family of HEDT processors and is supported by processors based on the Zen and Zen+ microarchitectures. Physically, the package is identical to the one used for Socket SP3 for their EPYC processors, however the features are much reduced.

Supported Processors

Package Diagram

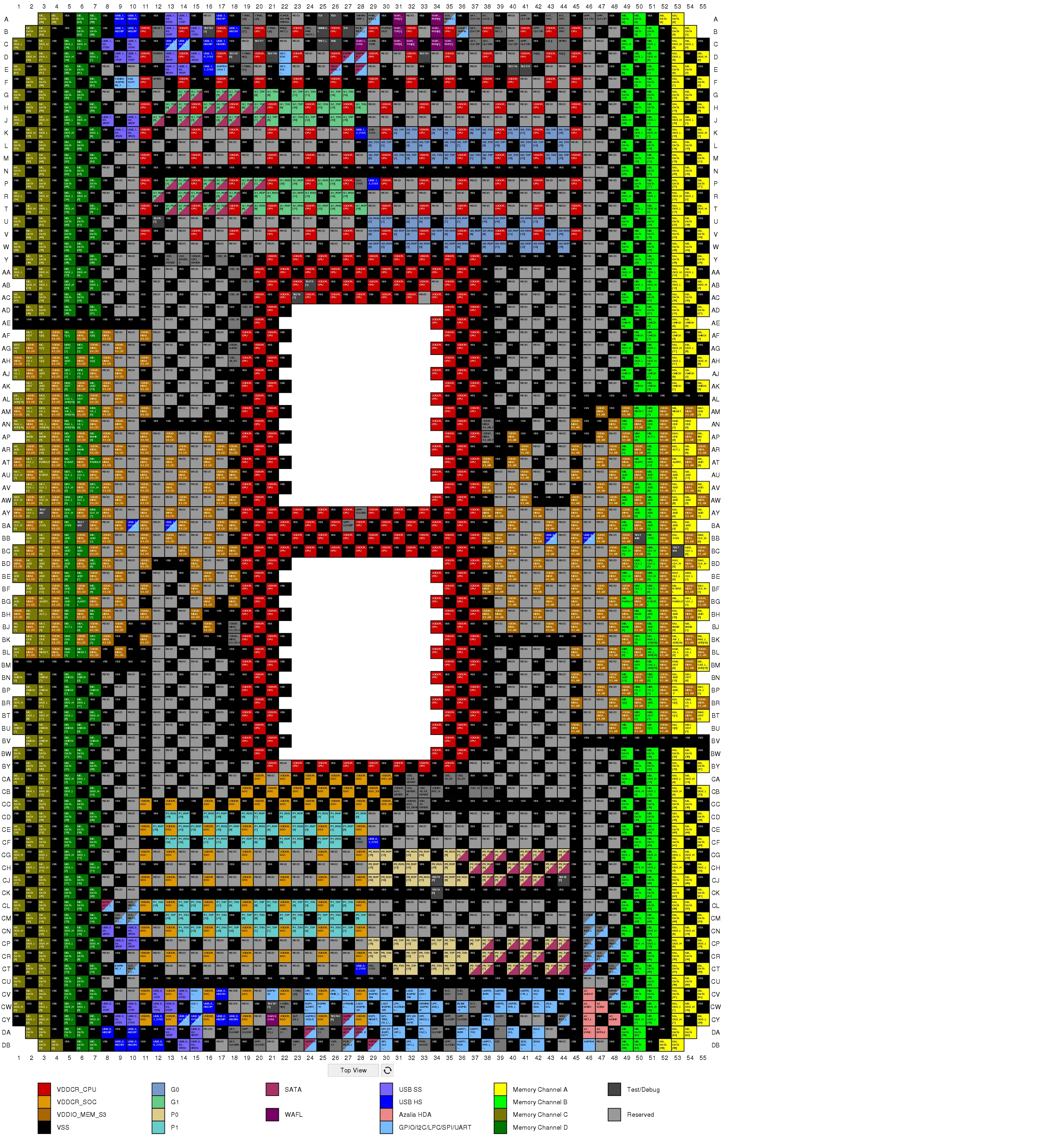

Pin Map

Socket SP3/TR4 Differences

| Pin | Socket SP3r1 | Socket SP3r2/TR4 |

|---|---|---|

| E25 | AGPIO23_1/SGPIO1_LOAD/MDIO3_SDA | RSVD |

| E28 | AGPIO23_2/SGPIO2_LOAD/MDIO5_SDA | EGPIO23_1/SGPIO1_LOAD/MDIO3_SDA |

| CY42 | AGPIO23_3/SGPIO3_LOAD/MDIO7_SDA | RSVD |

| D24 | AGPIO40_1/SGPIO1_DATAIN/MDIO2_SDA | RSVD |

| D27 | AGPIO40_2/SGPIO2_DATAIN/MDIO4_SDA | EGPIO40_1/SGPIO1_DATAIN/MDIO2_SDA |

| DB44 | AGPIO40_3/SGPIO3_DATAIN/MDIO6_SDA | RSVD |

| D25 | AGPIO9_1/SGPIO1_DATAOUT/MDIO3_SCL | RSVD |

| D28 | AGPIO9_2/SGPIO2_DATAOUT/MDIO5_SCL | EGPIO9_1/SGPIO1_DATAOUT/MDIO3_SCL |

| CY41 | AGPIO9_3/SGPIO3_DATAOUT/MDIO7_SCL | RSVD |

| E40 | BP0 | TEST14 |

| E41 | BP1 | TEST15 |

| D21 | BP2 | TEST16 |

| C20 | BP3 | TEST17 |

| C22 | BP4 | RSVD |

| C23 | BP5 | RSVD |

| misc. | G1 interface | All pins RSVD |

| P29 | G1B_ZVSS | USB_1_3_ZVSS |

| misc. | G2 interface | G1 interface |

| misc. | G3 interface | All pins RSVD |

| K28 | G3A_ZVSS | USB_1_2_ZVSS |

| DB20 | GPP_CLK0BN | GPP_CLK01N |

| DA19 | GPP_CLK0BP | GPP_CLK01P |

| DB18 | GPP_CLK0TN | GPP_CLK10N |

| DA18 | GPP_CLK0TP | GPP_CLK10P |

| B42 | GPP_CLK1BN | GPP_CLK13N |

| A41 | GPP_CLK1BP | GPP_CLK13P |

| C41 | GPP_CLK1TN | GPP_CLK12N |

| C40 | GPP_CLK1TP | GPP_CLK12P |

| A37 | GPP_CLK2BN | GFX_CLK11N |

| B37 | GPP_CLK2BP | GFX_CLK11P |

| C38 | GPP_CLK2TN | GFX_CLK10N |

| C37 | GPP_CLK2TP | GFX_CLK10P |

| DB35 | GPP_CLK3BN | GPP_CLK03N |

| DA34 | GPP_CLK3BP | GPP_CLK03P |

| CY36 | GPP_CLK3TN | GPP_CLK02N |

| CY35 | GPP_CLK3TP | GPP_CLK02P |

| misc. | Memory channel B | All pins RSVD with the following exceptions |

| AR40 | MB0_CKE[0] (DRAM Clock Enable) | VSS |

| AP41 | MB0_CKE[1] | VSS |

| AT39 | MB1_CKE[0] | VSS |

| AR39 | MB1_CKE[1] | VSS |

| BB43 | MB_ANALOGOUT | USB_0_OC3_L/AGPIO24_0 |

| AP39 | MB_RESET_L | VSS |

| misc. | Memory channel C | All pins RSVD with the following exceptions |

| AN47 | MC0_CKE[0] | VSS |

| AM48 | MC0_CKE[1] | VSS |

| AP46 | MC1_CKE[0] | VSS |

| AN46 | MC1_CKE[1] | VSS |

| BB46 | MC_ANALOGOUT | USB_0_OC2_L/AGPIO18_0 |

| A47 | MC_DATA[0] | GPP_CLK11P |

| CM46 | MC_DATA[49] | FANIN0/AGPIO84_0/NMI |

| CT48 | MC_DATA[50] | CLK_REQ0_0_L/AGPIO92_0 |

| CT46 | MC_DATA[51] | SATA_ACT_0_L/AGPIO130_0 |

| CR47 | MC_DATA[54] | CLK_REQ2_0_L/AGPIO116_0 |

| CR46 | MC_DATA[55] | CLK_REQG_0_L/OSCIN/EGPIO132_0 |

| CV48 | MC_DATA[56] | SPKR/AGPIO91 |

| CV46 | MC_DATA[57] | AZ_SDOUT |

| DA46 | MC_DATA[58] | AZ_SYNC |

| DB46 | MC_DATA[59] | AGPIO8 |

| A46 | MC_DATA[5] | GPP_CLK11N |

| DA47 | MC_DATA[62] | AZ_BITCLK |

| CN47 | MC_DQS_H[15] | FANOUT0/AGPIO85_0 |

| CW47 | MC_DQS_H[16] | AZ_SDIN2 |

| CP46 | MC_DQS_H[6] | CLK_REQ3_0_L/EGPIO131_0 |

| CY46 | MC_DQS_H[7] | AZ_RST_L |

| CP48 | MC_DQS_L[15] | CLK_REQ1_0_L/AGPIO115_0 |

| CY48 | MC_DQS_L[16] | AZ_SDIN0 |

| CN46 | MC_DQS_L[6] | GENINT2_L/AGPIO90 |

| CW46 | MC_DQS_L[7] | AZ_SDIN1 |

| AM46 | MC_RESET_L | VSS |

| misc. | Memory channel D | Memory channel B |

| misc. | Memory channel E | Memory channel C |

| misc. | Memory channel F | All pins RSVD with the following exceptions |

| BH16 | MF0_CKE[0] | VSS |

| BJ15 | MF0_CKE[1] | VSS |

| BG17 | MF1_CKE[0] | VSS |

| BH17 | MF1_CKE[1] | VSS |

| BA13 | MF_ANALOGOUT | USB_1_OC3_L/EGPIO24_1 |

| BJ17 | MF_RESET_L | VSS |

| misc. | Memory channel G | All pins RSVD with the following exceptions |

| BK9 | MG0_CKE[0] | VSS |

| BL8 | MG0_CKE[1] | VSS |

| BJ10 | MG1_CKE[0] | VSS |

| BK10 | MG1_CKE[1] | VSS |

| BA10 | MG_ANALOGOUT | USB_1_OC2_L/EGPIO18_1 |

| DB9 | MG_DATA[0] | USB_0_HSD3N |

| CL10 | MG_DATA[10] | CLK_REQG_1_L/EGPIO132_1 |

| CL8 | MG_DATA[11] | SATA_ACT_1_L/EGPIO130_1 |

| CT10 | MG_DATA[12] | CLK_REQ3_1_L/EGPIO131_1 |

| CT9 | MG_DATA[13] | EGPIO92_1 |

| CM10 | MG_DATA[14] | CLK_REQ2_1_L/EGPIO116_1 |

| CM9 | MG_DATA[15] | CLK_REQ1_1_L/EGPIO115_1 |

| DA8 | MG_DATA[1] | USB_0_HSD3P |

| DA10 | MG_DATA[4] | USB_0_HSD2P |

| B10 | MG_DATA[58] | USB_1_HSD2P |

| A10 | MG_DATA[59] | USB_1_HSD2N |

| DB10 | MG_DATA[5] | USB_0_HSD2N |

| F9 | MG_DATA[60] | FANIN1/EGPIO84_1 |

| F10 | MG_DATA[61] | FANOUT1/EGPIO85_1 |

| B9 | MG_DATA[62] | USB_1_HSD3P |

| A9 | MG_DATA[63] | USB_1_HSD3N |

| CW8 | MG_DQS_H[0] | USB_0_SS_3TXP |

| CP10 | MG_DQS_H[10] | USB_0_SS_2RXP |

| K9 | MG_DQS_H[15] | USB_1_SS_2RXN |

| D9 | MG_DQS_H[16] | USB_1_SS_2TXP |

| CN8 | MG_DQS_H[1] | USB_0_SS_3RXN |

| J10 | MG_DQS_H[6] | USB_1_SS_3RXP |

| C10 | MG_DQS_H[7] | USB_1_SS_3TXN |

| CY10 | MG_DQS_H[9] | USB_0_SS_2TXN |

| CY9 | MG_DQS_L[0] | USB_0_SS_3TXN |

| CN10 | MG_DQS_L[10] | USB_0_SS_2RXN |

| J8 | MG_DQS_L[15] | USB_1_SS_2RXP |

| C8 | MG_DQS_L[16] | USB_1_SS_2TXN |

| CP9 | MG_DQS_L[1] | USB_0_SS_3RXP |

| K10 | MG_DQS_L[6] | USB_1_SS_3RXN |

| D10 | MG_DQS_L[7] | USB_1_SS_3TXP |

| CW10 | MG_DQS_L[9] | USB_0_SS_2TXP |

| BL10 | MG_RESET_L | VSS |

| misc. | Memory channel H | Memory channel D |

| misc. | P1 interface | All pins RSVD |

| CF29 | P1A_ZVSS | USB_0_3_ZVSS |

| misc. | P2 interface | P1 interface |

| misc. | P3 interface | All pins RSVD |

| CT28 | P3B_ZVSS | USB_0_2_ZVSS |

| A23 | PCIE_RST1_L/EGPIO26_1 | RSVD |

| B28 | PCIE_RST2_L/EGPIO26_2 | PCIE_RST1_L/EGPIO26_1 |

| DB21 | PCIE_RST3_L/EGPIO26_3 | RSVD |

| CY44 | PM_INTR_L/AGPIO89 | GENINT1_L/AGPIO89 |

| AY28 | REFCLK100SSC_N | GPP_CLK00N |

| BA27 | REFCLK100SSC_P | GPP_CLK00P |

| E23 | S0A3_GPIO_1/AGPIO10_1/SGPIO1_CLK/MDIO2_SCL | RSVD |

| E26 | S0A3_GPIO_2/AGPIO10_2/SGPIO2_CLK/MDIO4_SCL | S0A3_GPIO_1/EGPIO10_1/SGPIO1_CLK/MDIO2_SCL |

| DA43 | S0A3_GPIO_3/AGPIO10_3/SGPIO3_CLK/MDIO6_SCL | RSVD |

| D34 | TEST41[1] | RSVD |

| B16 | TEST41[2] | TEST41[1] |

| CY20 | TEST41[3] | RSVD |

| CW36 | TEST47[0] | BLINK/AGPIO11 |

| E29 | TEST47[1] | RSVD |

| D18 | TEST47[2] | TEST47[0] |

| CW21 | TEST47[3] | TEST47[1] |

| AC33 | TEST4[1] | RSVD |

| AC23 | TEST4[2] | TEST4[1] |

| CA21 | TEST4[3] | RSVD |

| AB34 | TEST5[1] | RSVD |

| AB24 | TEST5[2] | TEST5[1] |

| BY22 | TEST5[3] | RSVD |

| DB12 | USB0_0_ZVSS | USB_0_0_ZVSS |

| CY12 | USB1_0_ZVSS | USB_0_1_ZVSS |

| D16 | USB2_1_ZVSS | USB_1_0_ZVSS |

| E16 | USB3_1_ZVSS | USB_1_1_ZVSS |

| C17 | USB_1_HSD2N | USB_1_HSD0N |

| C16 | USB_1_HSD2P | USB_1_HSD0P |

| B18 | USB_1_HSD3N | USB_1_HSD1N |

| A17 | USB_1_HSD3P | USB_1_HSD1P |

| E13 | USB_1_SS_2RXN | USB_1_SS_0RXN |

| D13 | USB_1_SS_2RXP | USB_1_SS_0RXP |

| A13 | USB_1_SS_2TXN | USB_1_SS_0TXN |

| B13 | USB_1_SS_2TXP | USB_1_SS_0TXP |

| D15 | USB_1_SS_3RXN | USB_1_SS_1RXN |

| E14 | USB_1_SS_3RXP | USB_1_SS_1RXP |

| B15 | USB_1_SS_3TXN | USB_1_SS_1TXN |

| A14 | USB_1_SS_3TXP | USB_1_SS_1TXP |

| CY15 | USB_OC0_L/AGPIO16_0 | USB_0_OC0_L/AGPIO16_0 |

| CY14 | USB_OC1_L/AGPIO17_0 | USB_0_OC1_L/AGPIO17_0 |

| C13 | USB_OC2_L/EGPIO16_1 | USB_1_OC0_L/EGPIO16_1 |

| C14 | USB_OC3_L/EGPIO17_1 | USB_1_OC1_L/EGPIO17_1 |

| misc. | VDDIO_MEM_S3_ABCD | VDDIO_MEM_S3_AB |

| AP38 | VDDIO_MEM_S3_ABCD_FB_H | VDDIO_MEM_S3_AB_FB_H |

| AN38 | VDDIO_MEM_S3_ABCD_FB_L | VDDIO_MEM_S3_AB_FB_L |

| misc. | VDDIO_MEM_S3_EFGH | VDDIO_MEM_S3_CD |

| BJ18 | VDDIO_MEM_S3_EFGH_FB_H | VDDIO_MEM_S3_CD_FB_H |

| BK18 | VDDIO_MEM_S3_EFGH_FB_L | VDDIO_MEM_S3_CD_FB_L |

| AG18 | VDD_18_S5_1 | VDDIO_AUDIO |

| F12 | VSS | SP3R2 |

| A16 | WAFL1_ZVSS | RSVD |

| C28 | WAFL2_ZVSS | WAFL1_ZVSS |

| DB17 | WAFL3_ZVSS | RSVD |

| E43 | X156M_H[1] | RSVD |

| F44 | X156M_L[1] | RSVD |

| D19 | X156M_H[2] | X156M_H[1] |

| E19 | X156M_L[2] | X156M_L[1] |

| CW19 | X156M_H[3] | RSVD |

| CV20 | X156M_L[3] | RSVD |

Bibliography

- David. S. (March 2018). "ISSCC 2018: AMD’s Zeppelin; Multi-chip routing and packaging"

- "Thermal Design Guide for Socket SP3 Processors", AMD Publ. #55423, Rev. 3.00, November 2017

See also

Facts about "Socket TR4 (SP3r2, sTR4) - Packages - AMD"

| designer | AMD + |

| first announced | May 16, 2017 + |

| first launched | August 10, 2017 + |

| instance of | package + |

| market segment | Desktop + |

| microarchitecture | Zen + and Zen+ + |

| name | Socket TR4 + |

| package | FCLGA-4094 + |

| package contacts | 4,094 + |

| package length | 58.5 mm (5.85 cm, 2.303 in) + |

| package pitch | 1 mm (0.0394 in) + |

| package type | Organic Flip-Chip Land Grid Array + |

| package width | 75.4 mm (7.54 cm, 2.969 in) + |

| socket | Socket TR4 +, sTR4 + and Socket SP3r2 + |

| tdp | 180 W (180,000 mW, 0.241 hp, 0.18 kW) + and 250 W (250,000 mW, 0.335 hp, 0.25 kW) + |