From WikiChip

Difference between revisions of "intel/microarchitectures/knights ferry"

| Line 11: | Line 11: | ||

|isa=x86 | |isa=x86 | ||

|extension=L1OM | |extension=L1OM | ||

| − | |predecessor | + | |predecessor=Rock Creek |

| − | + | |predecessor link=intel/microarchitectures/rock creek | |

| − | |||

| − | |predecessor | ||

|successor=Knights Corner | |successor=Knights Corner | ||

|successor link=intel/microarchitectures/knights_corner | |successor link=intel/microarchitectures/knights_corner | ||

Revision as of 01:53, 31 March 2019

| Edit Values | |

| Knights Ferry µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | May 31, 2010 |

| Phase-out | 2011 |

| Process | 45 nm |

| Core Configs | 32 |

| Instructions | |

| ISA | x86 |

| Extensions | L1OM |

| Succession | |

Knights Ferry (KNF) was the successor to Rock Creek, a 45 nm many-core microarchitecture designed by intel for high performance computing.

Note that Intel gave the PCIe expansion card the codename Aubrey Isle (die, components, board).

Architecture

Key changes from Larrabee

| This section is empty; you can help add the missing info by editing this page. |

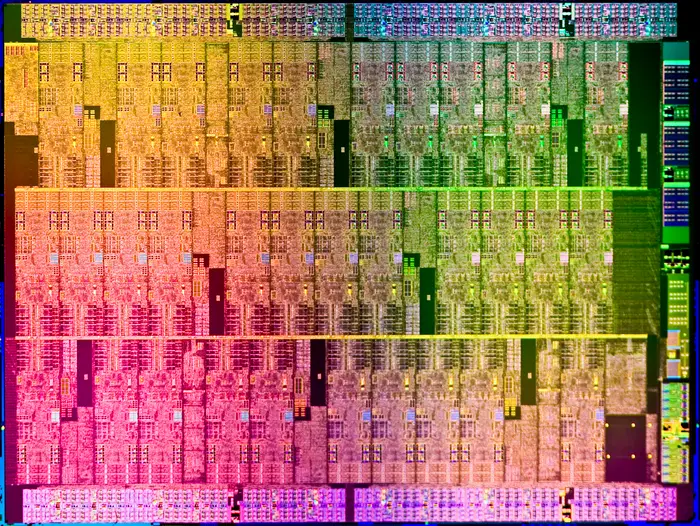

Die

Documents

Facts about "Knights Ferry - Microarchitectures - Intel"

| codename | Knights Ferry + |

| core count | 32 + |

| designer | Intel + |

| first launched | May 31, 2010 + |

| full page name | intel/microarchitectures/knights ferry + |

| instance of | microarchitecture + |

| instruction set architecture | x86 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Knights Ferry + |

| phase-out | 2011 + |

| process | 45 nm (0.045 μm, 4.5e-5 mm) + |