| Line 1: | Line 1: | ||

| − | {{title|Summit (OLCF-4)}} | + | {{title|Summit Supercomputer (OLCF-4)}} |

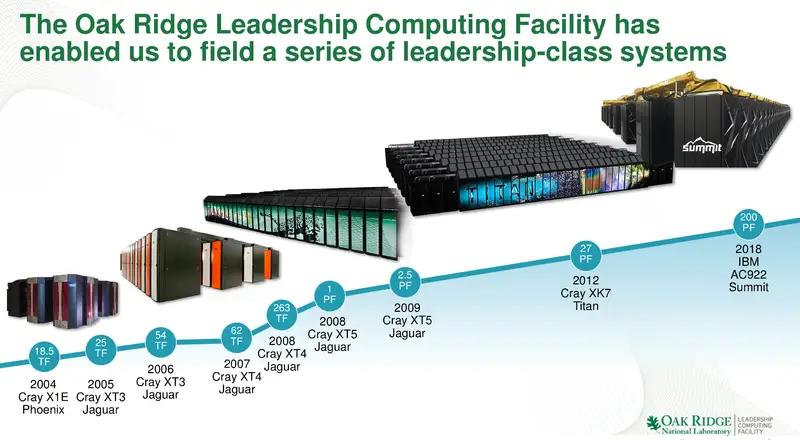

'''Summit''' ('''OLCF-4''') is {{\\|Titan|Titan's}} successor, a 200-petaFLOP [[supercomputer]] operating by the [[DoE]] [[Oak Ridge National Laboratory]]. Summit was officially unveiled on June 8, 2018 as the fastest supercomputer in the world, overtaking {{sc|Sunway TaihuLight}}. Summit is expected to be succeeded by {{\\|Frontier}} in 2021. | '''Summit''' ('''OLCF-4''') is {{\\|Titan|Titan's}} successor, a 200-petaFLOP [[supercomputer]] operating by the [[DoE]] [[Oak Ridge National Laboratory]]. Summit was officially unveiled on June 8, 2018 as the fastest supercomputer in the world, overtaking {{sc|Sunway TaihuLight}}. Summit is expected to be succeeded by {{\\|Frontier}} in 2021. | ||

Revision as of 10:52, 16 June 2018

Summit (OLCF-4) is Titan's successor, a 200-petaFLOP supercomputer operating by the DoE Oak Ridge National Laboratory. Summit was officially unveiled on June 8, 2018 as the fastest supercomputer in the world, overtaking Sunway TaihuLight. Summit is expected to be succeeded by Frontier in 2021.

Contents

History

Summit is one of three systems as part of the Collaboration of Oak Ridge, Argonne, and Lawrence Livermore Labs (CORAL) procurement program. Research and planning started in 2012 with initial system delivery arriving in late 2017. The full system arrived in early 2018 and the system was officially unveiled on June 8, 2018. Summit is estimated to have cost around $200 million as part of the CORAL procurement program.

Overview

Summit was designed to deliver 5-10x improvement in performance for real big science workload performance over Titan. Compared to Titan which had 18,688 nodes (AMD Opteron + Nvidia Kepler) with a 9 MW power consumption, Summit slightly increased the power consumption to 13 MW, reduced the number of nodes to only 4,608, but tenfold the peak theoretical performance from 27 petaFLOPS to around 225 PF.

Summit has over 200 petaFLOPS of theoretical compute power and over 3 AI exaFLOPS for AI workloads.

| Components | System | ||||||

|---|---|---|---|---|---|---|---|

| Processor | CPU | GPU | Rack | Compute Racks | Storage Racks | Switch Racks | |

| Type | POWER9 | V100 | Type | AC922 | SSC (4 ESS GL4) | Mellanox IB EDR | |

| Count | 9,216 2 × 18 x 256 | 27,648 6 × 18 x 256 | Count | 256 Racks × 18 Nodes | 40 Racks × 8 Servers | 18 Racks | |

| Peak FLOPS | 9.96 PF | 215.7 PF | Power | 59 kW | 38 kW | ||

| Peak AI FLOPS | 3.456 EF | 13 MW (Total System) | |||||

Summit has over 10 petabytes of memory.

| Summit Total Memory | |||

|---|---|---|---|

| Type | DDR4 | HBM2 | NVMe |

| Node | 512 GiB | 96 GiB | 1.6 GB |

| Summit | 2.53 PiB | 475 TiB | 7.37 PB |

Architecture

System

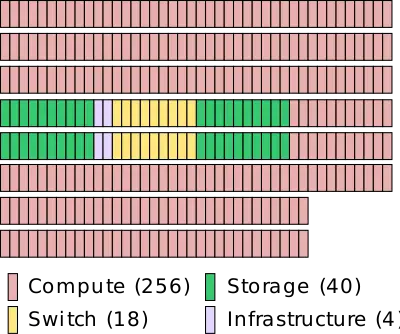

Weighing over 340 tons, Summit takes up 5,600 sq. ft. of floor space at Oak Ridge National Laboratory. Summit consists of 256 compute racks, 40 storage racks, 18 switching director racks, and 4 infrastructure racks. Servers are linked via Mellanox IB EDR interconnect in a three-level non-blocking fat-tree topology.

Compute Rack

Each of Summit's 256 Compute Racks consists of 18 Compute Nodes along with a Mellanox IB EDR for a non-blocking fat-tree interconnect topology (actually appears to be pruned 3-level fat-trees). With 18 nodes, each rack has 9 TiB of DDR4 memory and another 1.7 TiB of HBM2 memory for a total of 10.7 TiB of memory. A rack has a 59 kW max power and a total of 864 TF/s of peak compute power (ORNL reports 775 TF/s).

Compute Node

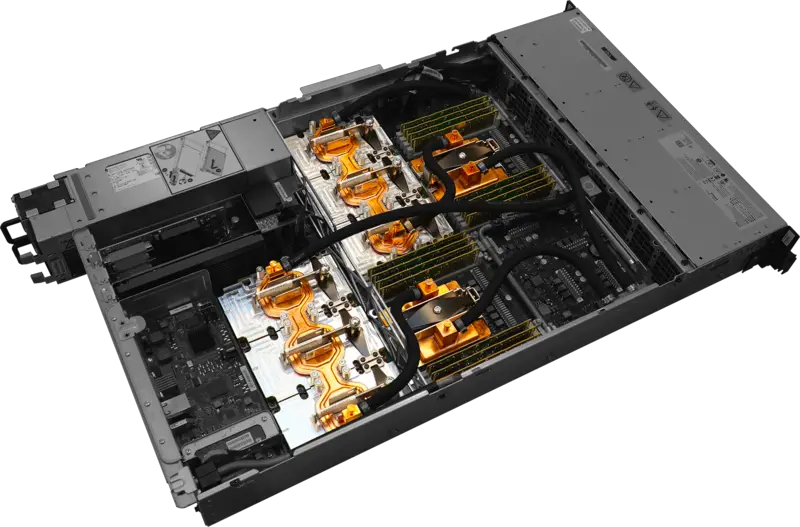

The basic compute node is the Power Systems AC922 (Accelerated Computing), formerly codename Witherspoon. The AC9222 comes in a 19-inch 2U rack-mount case.

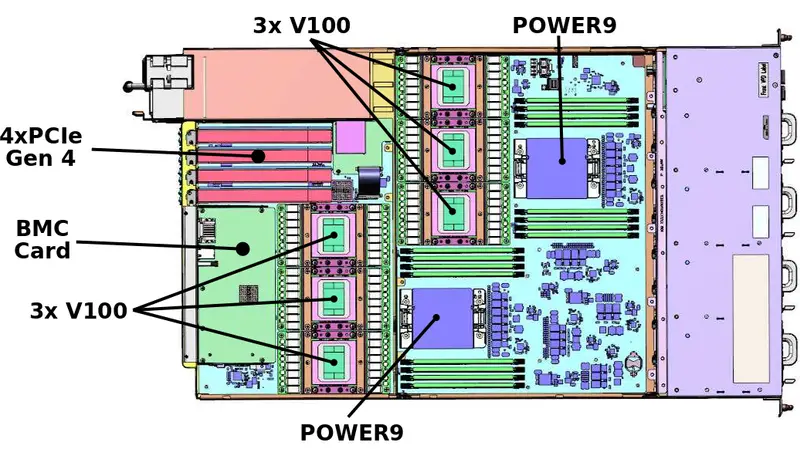

Each node has two 2200W power supplies, 4 PCIe Gen 4 slots, and a BMC card. There are two 22-core POWER9 processors per node, each with 8 DIMMs. For the Summit supercomputer, there are 8 32-GiB DDR4-2666 DIMMs for a total of 256 GiB and 170.7 GB/s of aggregated memory bandwidth per socket. There are three V100 GPUs per POWER9 socket. Those use the SXM2 form factor and come with 16 GiB of HBM2 memory for a total of 48 GiB of HBM2 and 2.7 TBps of aggregated bandwidth per socket.

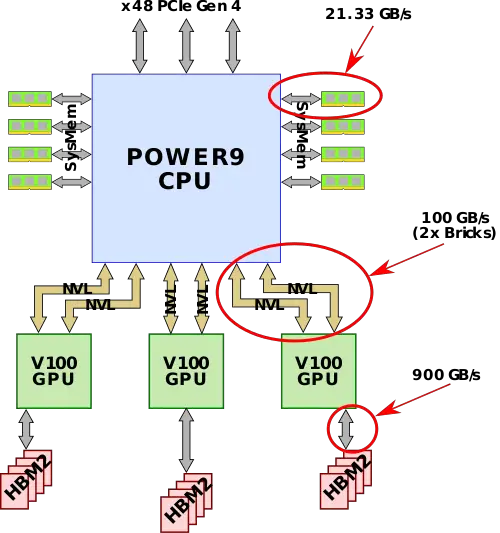

Socket

Since IBM POWER9 processors have native on-die NVLink connectivity, they are connected directly to the CPUs. The POWER9 processor has six NVLink 2.0 Bricks which are divided into three groups of two Bricks. Since NVLink 2.0 has bumped the signaling rate to 25 GT/s, two Bricks allow for 100 GB/s of bandwidth between the CPU and GPU. In addition to everything else, there are x48 PCIe Gen 4 lanes for I/O.

The Volta GPUs have 6 NVLink 2.0 Bricks which are divided into three groups. One group is used for the CPU while the other two groups interconnect every GPU to every other GPU. As with the GPU-CPU link, the aggregated bandwidth between two GPUs is also 100 GB/s.

| Single-socket Capabilities | ||||

|---|---|---|---|---|

| Processor | POWER9 | V100 | ||

| Count | 1 | 3 | ||

| FLOPS (SP) | 1.081 TFLOPS 22 × 49.12 GFLOPs | 47.1 TFLOPS 3 × 15.7 TFLOPs | ||

| FLOPS (DP) | 540.3 GFLOPs 22 × 24.56 GFLOPs | 23.4 TFLOPS 3 × 7.8 TFLOPs | ||

| AI FLOPS | - | 375 TFLOPS 3 × 125 TFLOPs | ||

| Memory | 256 GiB (DRR4) 8 × 32 GiB | 48 GiB (HBM2) 3 × 16 GiB | ||

| Bandwidth | 170.7 GB/s 8 × 21.33 GB/s | 900 GB/s/GPU | ||

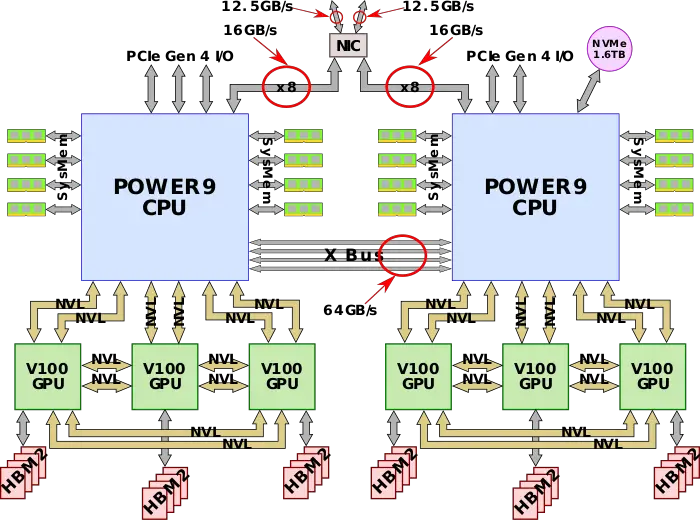

Full-node

There are two sockets per node. Communication between the two POWER9 processors is done over IBM’s X Bus. The X Bus is a 4-byte 16 GT/s link providing 64 GB/s of bidirectional bandwidth. A node has four PCIe Gen 4 slots consisting of two x16 (with CAPI support), a single x8 (also with CAPI support), and a single x4 slot. One of the x16 comes from one CPU, the other comes from the second. The x8 is configurable from either one of the CPUs and the last x4 slot comes from the second CPU only. The rest of the PCIe lanes used for various I/O applications (PEX, USB, BMC, and 1 Gbps Ethernet). Mellanox InfiniBand ConnectX5 (IB EDR) NIC which supports 100 Gbps of bi-directional traffic. This card sits on a PCIe Gen4 x8 shared slot which directly connects x8 lanes to each of the two processors. This enables each CPU to have direct access to the InfiniBand card, reducing bottlenecks.

Each POWER9 processor operates at 3.07 GHz and supports simultaneous execution of two vector single-precision operations. In other words, each core can execute 16 single-precision floating-point operations per cycle. At 3.07 GHz, this works out to 49.12 gigaFLOPS of peak theoretical performance per core. A full node has a little under 1.1 teraFLOPS (DP) of peak performance from the CPUs and around 47 teraFLOPS (DP) from the GPUs. Note that there is a slight discrepancy between our numbers and ORNL’s. Buddy Bland, OLCF Program Director, informed us that their peak performance for Summit only include the GPU’s peak performance numbers because that’s what most of the FP-intensive code will use to achieve the highest performance. In theory, if we were to include everything, Summit actually has a higher peak performance of around ~220 petaFLOPS.

There is 1.6 TB of NVMe Flash adapter attached to each node and Mellanox Infiniband EDR NIC.

| Full Node Capabilities | ||||

|---|---|---|---|---|

| Processor | POWER9 | V100 | ||

| Count | 2 | 6 | ||

| FLOPS (SP) | 2.161 TFLOPS 2 × 22 × 49.12 GFLOPs | 94.2 TFLOPs 6 × 15.7 TFLOPs | ||

| FLOPS (DP) | 1.081 TFLOPS 2 × 22 × 24.56 GFLOPs | 46.8 TFLOPS 6 × 7.8 TFLOPs | ||

| AI FLOPS | - | 750 TFLOPS 6 × 125 TFLOPs | ||

| Memory | 512 GiB (DRR4) 16 × 32 GiB | 96 GiB (HBM2) 6 × 16 GiB | ||

| Bandwidth | 341.33 GB/s 16 × 21.33 GB/s | 900 GB/s/GPU | ||