From WikiChip

Difference between revisions of "cavium/microarchitectures/vulcan"

(outline) |

(→Die) |

||

| Line 55: | Line 55: | ||

== Die == | == Die == | ||

| − | + | * Broadcom's original die size was around 600 mm². It's unknown how much the die has changed when it was modified by Cavium. | |

| + | * TSMC's [[16 nm process]] | ||

| + | |||

| + | |||

| + | :[[File:cavium vulcan die.png|class=wikichip_ogimage|600px]] | ||

| + | |||

| + | |||

| + | :[[File:cavium vulcan die (annotated).png|600px]] | ||

== All Vulcan Chips == | == All Vulcan Chips == | ||

Revision as of 20:26, 27 May 2018

| Edit Values | |

| Vulcan µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Broadcomm |

| Manufacturer | TSMC |

| Introduction | 2018 |

| Process | 16 nm |

| Core Configs | 16, 20, 24, 28, 30, 32 |

| Pipeline | |

| Type | Superscalar, Superpipeline |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Stages | 13-15 |

| Decode | 4-way |

| Instructions | |

| ISA | ARMv8.1 |

| Extensions | NEON |

| Cache | |

| L1I Cache | 32 KiB/core 8-way set associative |

| L1D Cache | 32 KiB/core 8-way set associative |

| L2 Cache | 256 KiB/core 8-way set associative |

| L3 Cache | 1 MiB/core |

Vulcan is a 16 nm high-performance 64-bit ARM microarchitecture designed by Broadcom and later Cavium for the server market.

Introduced in 2018, Vulcan-based microprocessors are branded as part of the ThunderX2 family.

Contents

Architecture

| This section is empty; you can help add the missing info by editing this page. |

Block Diagram

| This section is empty; you can help add the missing info by editing this page. |

Memory Hierarchy

| This section is empty; you can help add the missing info by editing this page. |

Overview

| This section is empty; you can help add the missing info by editing this page. |

Core

| This section is empty; you can help add the missing info by editing this page. |

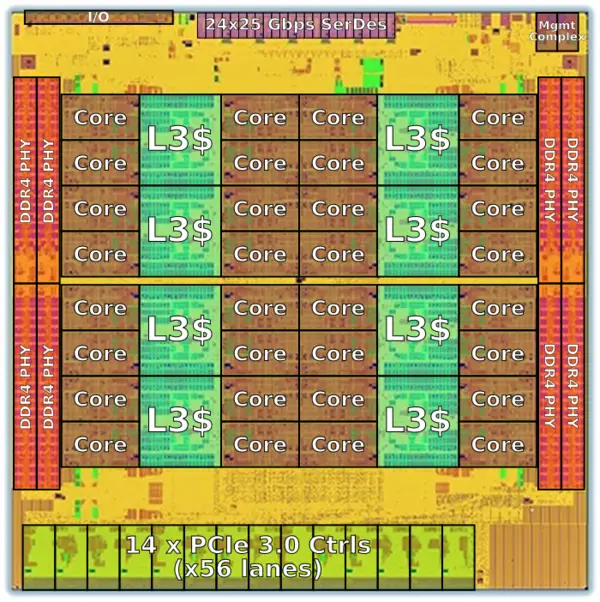

Die

- Broadcom's original die size was around 600 mm². It's unknown how much the die has changed when it was modified by Cavium.

- TSMC's 16 nm process

All Vulcan Chips

| This section is empty; you can help add the missing info by editing this page. |

References

- Some information was obtained directly from Broadcom

- Some information was obtained directly from Cavium

See also

Facts about "Vulcan - Microarchitectures - Cavium"

| codename | Vulcan + |

| core count | 16 +, 20 +, 24 +, 28 +, 30 + and 32 + |

| designer | Broadcomm + |

| first launched | 2018 + |

| full page name | cavium/microarchitectures/vulcan + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8.1 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Vulcan + |

| pipeline stages (max) | 15 + |

| pipeline stages (min) | 13 + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |