From WikiChip

Difference between revisions of "movidius/microarchitectures/shave v2.0"

(→Architecture) |

(→Instruction Set) |

||

| Line 35: | Line 35: | ||

** Instruction predication | ** Instruction predication | ||

** Large set of integer operations | ** Large set of integer operations | ||

| − | |||

* VLIW style | * VLIW style | ||

** Parallel functional units controlled by VLIW instructions | ** Parallel functional units controlled by VLIW instructions | ||

Revision as of 15:33, 11 March 2018

| Edit Values | |

| SHAVE v2.0 µarch | |

| General Info | |

| Arch Type | Accelerator |

| Designer | Movidius |

| Manufacturer | TSMC |

| Introduction | 2011 |

| Pipeline | |

| Type | VLIW |

Streaming Hybrid Architecture Vector Engine v2.0 (SHAVE v2.0) is an accelerator microarchitecture designed by Movidius for their vision processors. SHAVE is incorporated into Movidius Myriad family of vision processors.

Contents

History

The original SHAVE architecture was designed primarily for the acceleration of game physics. Low demand for expensive physics acceleration in smartphones has forced to re-focused on image and vision processing. Their architecture was versatile enough that it allowed for fairly simple modification to target machine vision processing.

Process Technology

- Main article: 65 nm lithography process

This microarchitecture was designed for TSMC's 65 nm process.

Architecture

- Hybrid RISC-DSP-GPU VLIW architecture

- 20 GFLOPS computational power

- At 300 mW

- Predicated execution

- Branch delay slots

- Tailored to streaming workloads

- 128-bit vector arithmetic

- 8/16/32-bit integer

- 16/32-bit floating point

- Full support for sparse data structures (matrix/array, random access)

Instruction Set

SHAVE supports a mixture of many different types of instructions belonging to a number of different classes of architectures.

- RISC style

- Instruction predication

- Large set of integer operations

- VLIW style

- Parallel functional units controlled by VLIW instructions

- 8/16/32-bit x 1-4 SIMD int

- DSP style

- Zero overhead looping

- Modulo addressing

- Transparent DMA modes

- FFT, Viterbi, etc..

- Parallel comparisons

- GPU style

- Streaming operations

- 16/32-bit FP operations

- Texture management unit

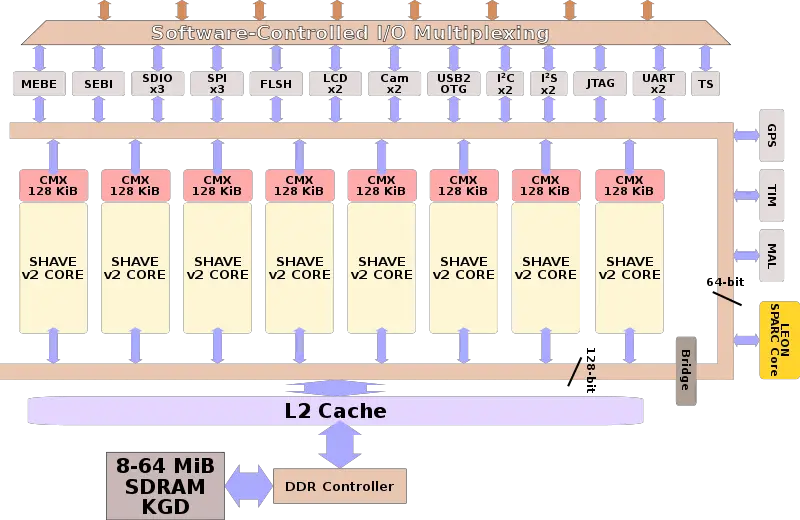

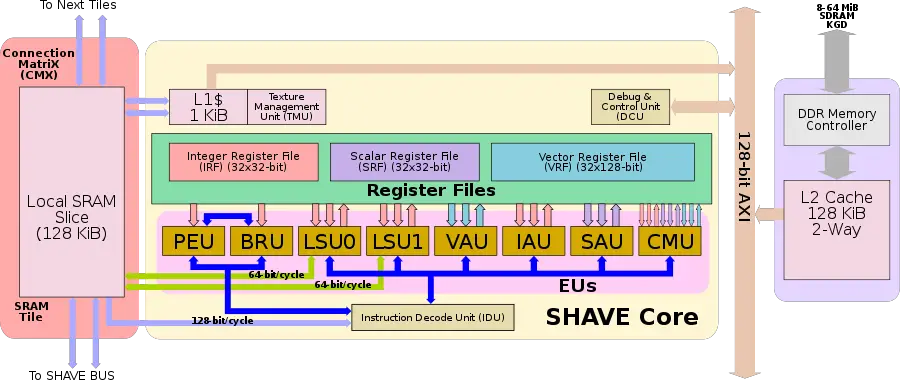

Block Diagram

Entire SoC

Individual Core

Facts about "SHAVE v2.0 - Microarchitectures - Intel Movidius"

| codename | SHAVE v2.0 + |

| designer | Movidius + |

| first launched | 2011 + |

| full page name | movidius/microarchitectures/shave v2.0 + |

| instance of | microarchitecture + |

| manufacturer | TSMC + |

| name | SHAVE v2.0 + |