From WikiChip

Difference between revisions of "movidius/myriad/ma1133"

(→Overview) |

|||

| Line 30: | Line 30: | ||

== Overview == | == Overview == | ||

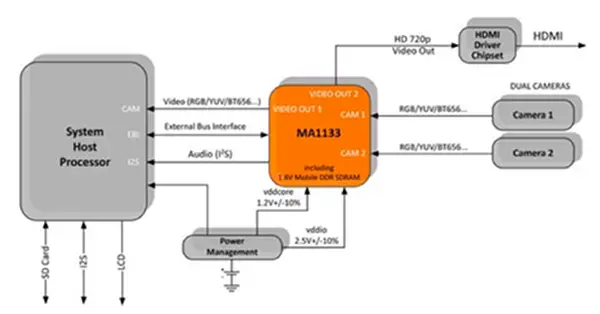

| − | The MA1133 is a vision [[accelerator]] designed to work alongside a main host processors, typically in a mobile or embedded device. The MA1133 consists of a single [[SPARC]] {{sparc|V8}} [[LEON3]] core which is used for management and control and eight {{movidius|SHAVE v2.0|l=arch}} core which are the workhorse of this chip. Each core has 128 KiB of cache. The eight SHAVE cores together are capable of 20GFLOPS of processing power at just a few 100s milliwatt of power. | + | The MA1133 is a vision [[accelerator]] designed to work alongside a main host processors, typically in a mobile or embedded device. The chip communicates directly with the camera and display components. |

| + | |||

| + | [[File:movidius ma1133 block.png|600px]] | ||

| + | |||

| + | The MA1133 consists of a single [[SPARC]] {{sparc|V8}} [[LEON3]] core which is used for management and control and eight {{movidius|SHAVE v2.0|l=arch}} core which are the workhorse of this chip. Each core has 128 KiB of cache. The eight SHAVE cores together are capable of 20GFLOPS of processing power at just a few 100s milliwatt of power. | ||

[[File:movidius ma1000 silicon platform.png|600px]] | [[File:movidius ma1000 silicon platform.png|600px]] | ||

Revision as of 12:10, 11 March 2018

| Edit Values | |

| Myriad 1 MA1133 | |

| General Info | |

| Designer | Movidius |

| Manufacturer | TSMC |

| Model Number | MA1133 |

| Market | Embedded, Mobile |

| Introduction | September, 2010 (announced) February, 2011 (launched) |

| General Specs | |

| Family | Myriad |

| Series | 1 |

| Frequency | 180 MHz |

| Microarchitecture | |

| ISA | SPARC V8 (SPARC), SHAVE (SHAVE) |

| Microarchitecture | LEON3, SHAVE v2.0 |

| Process | 65 nm |

| Technology | TSMC |

| Word Size | 32 bit |

| Cores | 9 |

| Threads | 9 |

| Electrical | |

| Vcore | 1.2 V |

| VI/O | 2.5 V |

Myriad 1 MA1133 was a vision processing accelerator designed by Movidius and introduced in 2010 designed to serve as a video streams accelerator for auto-stereoscopic screens for smartphones.

Overview

The MA1133 is a vision accelerator designed to work alongside a main host processors, typically in a mobile or embedded device. The chip communicates directly with the camera and display components.

The MA1133 consists of a single SPARC V8 LEON3 core which is used for management and control and eight SHAVE v2.0 core which are the workhorse of this chip. Each core has 128 KiB of cache. The eight SHAVE cores together are capable of 20GFLOPS of processing power at just a few 100s milliwatt of power.

Facts about "Myriad 1 MA1133 - Intel Movidius"

| base frequency | 180 MHz (0.18 GHz, 180,000 kHz) + |

| core count | 9 + |

| core voltage | 1.2 V (12 dV, 120 cV, 1,200 mV) + |

| designer | Movidius + |

| family | Myriad + |

| first announced | September 2010 + |

| first launched | February 2011 + |

| full page name | movidius/myriad/ma1133 + |

| instance of | microprocessor + |

| io voltage | 2.5 V (25 dV, 250 cV, 2,500 mV) + |

| isa | SPARC V8 + and SHAVE + |

| isa family | SPARC + and SHAVE + |

| ldate | February 2011 + |

| manufacturer | TSMC + |

| market segment | Embedded + and Mobile + |

| microarchitecture | LEON3 + and SHAVE v2.0 + |

| model number | MA1133 + |

| name | Myriad 1 MA1133 + |

| process | 65 nm (0.065 μm, 6.5e-5 mm) + |

| series | 1 + |

| thread count | 9 + |

| word size | 32 bit (4 octets, 8 nibbles) + |