From WikiChip

Difference between revisions of "intel/microarchitectures/cannon lake"

m (David moved page intel/microarchitectures/cannonlake to intel/microarchitectures/cannon lake) |

|||

| Line 1: | Line 1: | ||

| − | {{intel title| | + | {{intel title|Cannon Lake|arch}} |

{{microarchitecture | {{microarchitecture | ||

|atype=CPU | |atype=CPU | ||

| − | |name= | + | |name=Cannon Lake |

|designer=Intel | |designer=Intel | ||

|manufacturer=Intel | |manufacturer=Intel | ||

| Line 9: | Line 9: | ||

|isa=x86-64 | |isa=x86-64 | ||

| − | |core name= | + | |core name=Cannon Lake Y |

| − | |core name 2= | + | |core name 2=Cannon Lake U |

|predecessor=Kaby Lake | |predecessor=Kaby Lake | ||

|predecessor link=intel/microarchitectures/kaby lake | |predecessor link=intel/microarchitectures/kaby lake | ||

| Line 18: | Line 18: | ||

|succession=Yes | |succession=Yes | ||

}} | }} | ||

| − | ''' | + | '''Cannon Lake''' ('''CNL''') (formerly '''Skymont''') is a planned [[microarchitecture]] by [[Intel]] as a successor to {{\\|Kaby Lake}}. Cannon Lake is expected to be fabricated using a [[10 nm process]] and is set to be introduced in the fourth quarter of [[2017]]. Cannon Lake is the "Process" microarchitecture as part of Intel's {{intel|PAO}} model. |

| − | For mobile, | + | For mobile, Cannon Lake is expected to be branded as 8th Generation Intel {{intel|Core i3}}, {{intel|Core i5}}. and {{intel|Core i7}} processors. |

== Process Technology == | == Process Technology == | ||

| − | + | Cannon Lake is manufactured on Intel's [[10 nm process]] (P1274). Intel's 10 nm process is the first high-volume manufacturing process to employ [[Self-Aligned Quad Patterning]] (SAQP) (goes under the "Hyper-Scaling" marketing name). Intel's 10nm features a 0.0367 µm² [[SRAM]] bit cell. | |

[[Scaling]]: | [[Scaling]]: | ||

| Line 29: | Line 29: | ||

{| class="wikitable" | {| class="wikitable" | ||

|- | |- | ||

| − | ! !! Broadwell !! | + | ! !! Broadwell !! Cannon Lake !! Δ !! rowspan="8" | [[File:intel 10nm fin.png|250px]] |

|- | |- | ||

| || [[14 nm]] || [[10 nm]] || | | || [[14 nm]] || [[10 nm]] || | ||

| Line 53: | Line 53: | ||

! Core !! Abbrev !! Description !! Graphics !! Target | ! Core !! Abbrev !! Description !! Graphics !! Target | ||

|- | |- | ||

| − | | {{intel| | + | | {{intel|Cannon Lake Y|l=core}} || CNL-Y || Extremely low power || GT2 || 2-in-1s detachable, tablets, and computer sticks |

|- | |- | ||

| − | | {{intel| | + | | {{intel|Cannon Lake U|l=core}} || CNL-U || Ultra-low Power || GT2/GT3 || Light notebooks, portable All-in-Ones (AiOs), Minis, and conference room |

|- | |- | ||

| − | | {{intel| | + | | {{intel|Cannon Lake H|l=core}} || CNL-H || High-performance Graphics || GT2/GT3 || Ultimate mobile performance, mobile workstations |

|- | |- | ||

| − | | {{intel| | + | | {{intel|Cannon Lake S|l=core}} || CNL-S || Performance-optimized lifestyle || GT2/GT3 || Desktop performance to value, AiOs, and minis |

|- | |- | ||

| − | | {{intel| | + | | {{intel|Cannon Lake DT|l=core}} || CNL-DT || Workstation || GT2 || Workstations & entry-level servers |

|} | |} | ||

| Line 89: | Line 89: | ||

** {{intel|Iris Plus Graphics 650}} '''→''' {{intel|Iris Plus Graphics 750}} (unknown change) | ** {{intel|Iris Plus Graphics 650}} '''→''' {{intel|Iris Plus Graphics 750}} (unknown change) | ||

| − | == All | + | == All Cannon Lake Chips == |

<!-- NOTE: | <!-- NOTE: | ||

This table is generated automatically from the data in the actual articles. | This table is generated automatically from the data in the actual articles. | ||

| Line 99: | Line 99: | ||

{{comp table start}} | {{comp table start}} | ||

<table class="comptable sortable tc18 tc19 tc20 tc21 tc22 tc23"> | <table class="comptable sortable tc18 tc19 tc20 tc21 tc22 tc23"> | ||

| − | <tr class="comptable-header"><th> </th><th colspan="23"> | + | <tr class="comptable-header"><th> </th><th colspan="23">Cannon Lake Chips</th></tr> |

<tr class="comptable-header"><th> </th><th colspan="13">Main processor</th><th colspan="3">IGP</th><th colspan="7">Major Feature Diff</th></tr> | <tr class="comptable-header"><th> </th><th colspan="13">Main processor</th><th colspan="3">IGP</th><th colspan="7">Major Feature Diff</th></tr> | ||

<tr class="comptable-header"><th class="unsortable">Model</th><th>Launched</th><th>Price</th><th>Family</th><th>Platform</th><th>Core</th><th>C</th><th>T</th><th>L3$</th><th>L4$</th><th>TDP</th><th>Freq</th><th>Turbo</th><th>Max Mem</th><th>Name</th><th>Freq</th><th>Turbo</th><th>{{intel|turbo boost|TBT}}</th><th>HT</th><th>AVX2</th><th>TXT</th><th>TSX</th><th>vPro</th><th>VT-d</th></tr> | <tr class="comptable-header"><th class="unsortable">Model</th><th>Launched</th><th>Price</th><th>Family</th><th>Platform</th><th>Core</th><th>C</th><th>T</th><th>L3$</th><th>L4$</th><th>TDP</th><th>Freq</th><th>Turbo</th><th>Max Mem</th><th>Name</th><th>Freq</th><th>Turbo</th><th>{{intel|turbo boost|TBT}}</th><th>HT</th><th>AVX2</th><th>TXT</th><th>TSX</th><th>vPro</th><th>VT-d</th></tr> | ||

<tr class="comptable-header comptable-header-sep"><th> </th><th colspan="23">[[Uniprocessors]]</th></tr> | <tr class="comptable-header comptable-header-sep"><th> </th><th colspan="23">[[Uniprocessors]]</th></tr> | ||

| − | {{#ask: [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture:: | + | {{#ask: [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Cannon Lake]] [[max cpu count::1]] |

|?full page name | |?full page name | ||

|?model number | |?model number | ||

| Line 138: | Line 138: | ||

|limit=100 | |limit=100 | ||

}} | }} | ||

| − | <tr><th> </th><th colspan="23"><span style="font-size: 20px;">No | + | <tr><th> </th><th colspan="23"><span style="font-size: 20px;">No Cannon Lake Chips have been released yet.</span></th></tr> |

| − | {{comp table count|ask=[[Category:microprocessor models by intel]][[instance of::microprocessor]][[microarchitecture:: | + | {{comp table count|ask=[[Category:microprocessor models by intel]][[instance of::microprocessor]][[microarchitecture::Cannon Lake]]}} |

</table> | </table> | ||

{{comp table end}} | {{comp table end}} | ||

Revision as of 00:34, 13 December 2017

| Edit Values | |

| Cannon Lake µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | 2017 |

| Process | 10 nm |

| Instructions | |

| ISA | x86-64 |

| Cores | |

| Core Names | Cannon Lake Y, Cannon Lake U |

| Succession | |

Cannon Lake (CNL) (formerly Skymont) is a planned microarchitecture by Intel as a successor to Kaby Lake. Cannon Lake is expected to be fabricated using a 10 nm process and is set to be introduced in the fourth quarter of 2017. Cannon Lake is the "Process" microarchitecture as part of Intel's PAO model.

For mobile, Cannon Lake is expected to be branded as 8th Generation Intel Core i3, Core i5. and Core i7 processors.

Contents

Process Technology

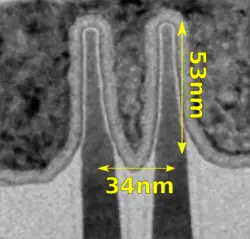

Cannon Lake is manufactured on Intel's 10 nm process (P1274). Intel's 10 nm process is the first high-volume manufacturing process to employ Self-Aligned Quad Patterning (SAQP) (goes under the "Hyper-Scaling" marketing name). Intel's 10nm features a 0.0367 µm² SRAM bit cell.

| Broadwell | Cannon Lake | Δ |

| |

|---|---|---|---|---|

| 14 nm | 10 nm | |||

| Fin Pitch | 42 nm | 34 | 0.81x | |

| Fin Width | 8 nm | ? nm | ?x | |

| Fin Height | 42 nm | 53 nm | 1.24x | |

| Gate Pitch | 70 nm | 54 nm | 0.77x | |

| Interconnect Pitch | 52 nm | 36 nm | 0.69x | |

| Cell Height | 399 nm | 272 nm | 0.68x |

Codenames

| Core | Abbrev | Description | Graphics | Target |

|---|---|---|---|---|

| Cannon Lake Y | CNL-Y | Extremely low power | GT2 | 2-in-1s detachable, tablets, and computer sticks |

| Cannon Lake U | CNL-U | Ultra-low Power | GT2/GT3 | Light notebooks, portable All-in-Ones (AiOs), Minis, and conference room |

| Cannon Lake H | CNL-H | High-performance Graphics | GT2/GT3 | Ultimate mobile performance, mobile workstations |

| Cannon Lake S | CNL-S | Performance-optimized lifestyle | GT2/GT3 | Desktop performance to value, AiOs, and minis |

| Cannon Lake DT | CNL-DT | Workstation | GT2 | Workstations & entry-level servers |

Architecture

| This section is empty; you can help add the missing info by editing this page. |

Key changes from Kaby Lake

- 10 nm process (from 14 nm)

- Mainstream chipset

- 200 Series chipset → 300 Series chipset

- Integrated Programmable (Open FW SDK) Quad-Core Audio DSP

- Soundwire Digital Audio Interface

- Integrated USB 3.1 (10 Gib/s)

- Up to 6 ports

- Integrated Intel wireless controller (IEEE 802.11ac)

- Integrated SDXC 3.0 controller

- Thunderbolt 3.0(Titan Ridge) with DisplayPort 1.4 support

- C10 & S0ix Support for Modern Standby

- 200 Series chipset → 300 Series chipset

- Gen9.5 → Gen10 graphics

- Gen10 GPUs

- HD Graphics 610 → HD Graphics 710 (24 Execution Units, 2x EUs from Kaby Lake)

- HD Graphics 615 → HD Graphics 715 (40 Execution Units, 1.7x EUs from Kaby Lake)

- HD Graphics 620 → HD Graphics 720 (40 Execution Units, 1.7x EUs from Kaby Lake)

- HD Graphics 630 → HD Graphics 730 (40 Execution Units, 1.7x EUs from Kaby Lake)

- HD Graphics P630 → HD Graphics P730 (40 Execution Units, 1.7x EUs from Kaby Lake)

- Iris Plus Graphics 640 → Iris Plus Graphics 740 (unknown change)

- Iris Plus Graphics 650 → Iris Plus Graphics 750 (unknown change)

All Cannon Lake Chips

| Cannon Lake Chips | |||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Main processor | IGP | Major Feature Diff | |||||||||||||||||||||

| Model | Launched | Price | Family | Platform | Core | C | T | L3$ | L4$ | TDP | Freq | Turbo | Max Mem | Name | Freq | Turbo | TBT | HT | AVX2 | TXT | TSX | vPro | VT-d |

| Uniprocessors | |||||||||||||||||||||||

| M3-8114Y | Core M3 | Cannon Lake Y | 2 | 4 | 1.5 GHz 1,500 MHz 1,500,000 kHz | 16 GiB 16,384 MiB 16,777,216 KiB 17,179,869,184 B 0.0156 TiB | UHD Graphics ? | 300 MHz 0.3 GHz 300,000 KHz | ✔ | ✔ | ✔ | ✘ | ✘ | ✘ | ✔ | ||||||||

| i3-8121U | 15 May 2018 | Core i3 | Cannon Lake U | 2 | 4 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 15 W 15,000 mW 0.0201 hp 0.015 kW | 2.2 GHz 2,200 MHz 2,200,000 kHz | 3.2 GHz 3,200 MHz 3,200,000 kHz | 32 GiB 32,768 MiB 33,554,432 KiB 34,359,738,368 B 0.0313 TiB | ✔ | ✔ | ✔ | ✘ | ✘ | ✘ | ✔ | ||||||

| No Cannon Lake Chips have been released yet. | |||||||||||||||||||||||

| Count: 2 | |||||||||||||||||||||||

References

- Mark Bohr, Intel. Intel Technology and Manufacturing Day. Mar 28, 2017.

See also

- AMD's Zen

Facts about "Cannon Lake - Microarchitectures - Intel"

| codename | Cannon Lake + |

| designer | Intel + |

| first launched | 2017 + |

| full page name | intel/microarchitectures/cannon lake + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Cannon Lake + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |