From WikiChip

Difference between revisions of "intel/microarchitectures/willow cove"

| Line 24: | Line 24: | ||

== Architecture == | == Architecture == | ||

Key changes from {{\\|Sunny Cove}} | Key changes from {{\\|Sunny Cove}} | ||

| − | * Expanded L2 Cache( | + | * Expanded L2 Cache( 512KB 8-way → 1.25MB 20-way) |

| − | * 50% Expanded L3 Cache ( | + | * 50% Expanded L3 Cache ( 8MB 16-way → 12MB 12-way) |

* Memory Subsystem with more bandwidth and LPDDR5 support | * Memory Subsystem with more bandwidth and LPDDR5 support | ||

* New Total Memory Encryption(TME) feature | * New Total Memory Encryption(TME) feature | ||

Revision as of 20:27, 6 October 2020

| Edit Values | |

| Willow Cove µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | 2020 |

| Process | 10 nm |

| Instructions | |

| ISA | x86-64 |

| Succession | |

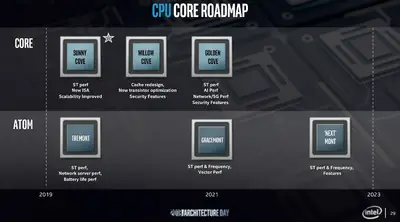

Willow Cove is the successor to Sunny Cove, a high-performance 10 nm x86 core microarchitecture designed by Intel for an array of server and client products, including Tiger Lake.

History

Willow Cove was originally unveiled by Intel at their 2018 architecture day. Willow Cove is intended to succeed Sunny Cove in the 2020 timeframe.

Process Technology

Willow Cove is designed to take advantage of Intel's 10 nm process (10nm SuperFin).

Architecture

Key changes from Sunny Cove

- Expanded L2 Cache( 512KB 8-way → 1.25MB 20-way)

- 50% Expanded L3 Cache ( 8MB 16-way → 12MB 12-way)

- Memory Subsystem with more bandwidth and LPDDR5 support

- New Total Memory Encryption(TME) feature

This list is incomplete; you can help by expanding it.

New instructions

Willow Cove introduced a number of new instructions:

- Control-flow Enforcement Technology (CET) enhancements

-

MOVDIR- Direct stores - Additional AVX-512 extensions:

-

AVX512_VP2INTERSECT- AVX-512 Vector Intersection Instructions

-

Only on server parts (Sapphire Rapids):

-

ENQCMD- Enqueue Stores - Intel Advanced Matrix Extensions (Intel AMX)

Bibliography

- Intel Architecture Day 2018, December 11, 2018

Facts about "Willow Cove - Microarchitectures - Intel"

| codename | Willow Cove + |

| designer | Intel + |

| first launched | 2020 + |

| full page name | intel/microarchitectures/willow cove + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Willow Cove + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |