From WikiChip

Difference between revisions of "centaur/microarchitectures/cha"

(→Architecture) |

|||

| Line 17: | Line 17: | ||

=== Key changes from {{\\|CN}} === | === Key changes from {{\\|CN}} === | ||

{{empty section}} | {{empty section}} | ||

| + | === Block Diagram === | ||

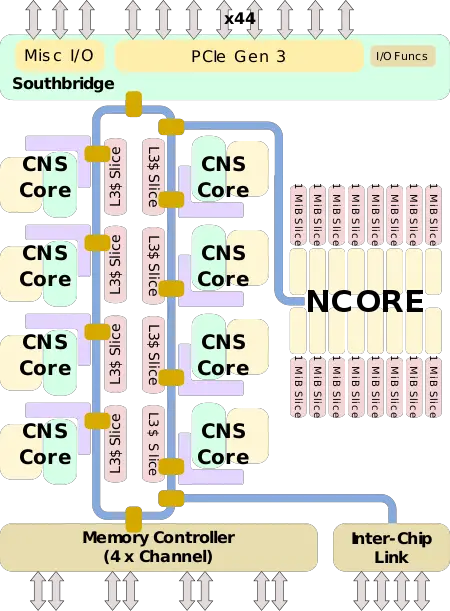

| + | ==== CHA SoC ==== | ||

| + | :[[File:cha soc block diagram.svg|450px]] | ||

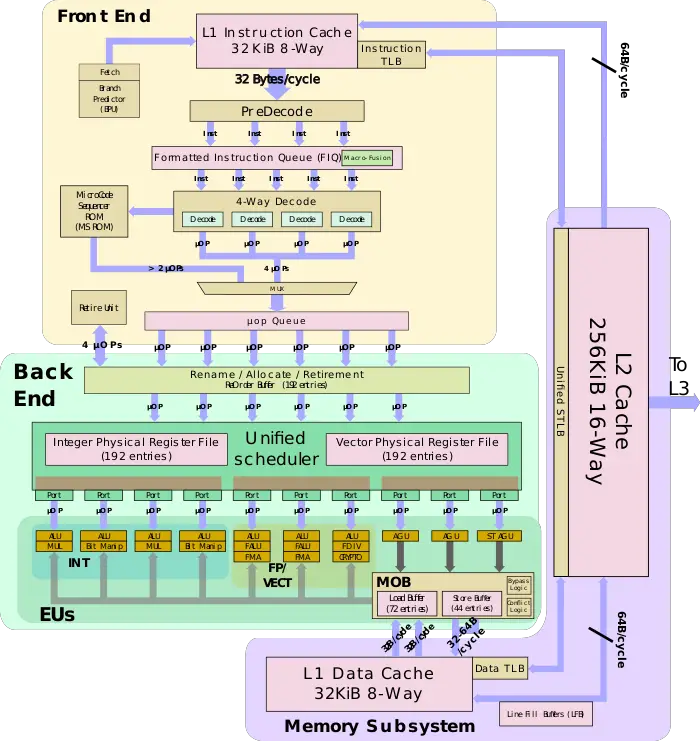

| + | ==== CNS Core ==== | ||

| + | :[[File:cns block diagram.svg|700px]] | ||

| + | ==== NCORE NPU ==== | ||

== Overview == | == Overview == | ||

Revision as of 17:37, 22 January 2020

| Edit Values | |

| CHA µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Centaur Technology |

| Manufacturer | TSMC |

| Process | 16 nm |

| Core Configs | 8 |

| Instructions | |

| ISA | x86-64 |

CHA is a 16-nanometer x86 SoC microarchitecture designed by Centaur Technology for the server market.

Contents

Process technology

| This section is empty; you can help add the missing info by editing this page. |

Architecture

Key changes from CN

| This section is empty; you can help add the missing info by editing this page. |

Block Diagram

CHA SoC

CNS Core

NCORE NPU

Overview

| This section is empty; you can help add the missing info by editing this page. |

CNS Core

| This section is empty; you can help add the missing info by editing this page. |

NCORE NPU

| This section is empty; you can help add the missing info by editing this page. |

Die

| This section is empty; you can help add the missing info by editing this page. |

Bibliography

- Centaur. personal communication. November 2019.

See also

- Direct Competition

Facts about "CHA - Microarchitectures - Centaur Technology"

| codename | CHA + |

| core count | 8 + |

| designer | Centaur Technology + |

| full page name | centaur/microarchitectures/cha + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | CHA + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |