(865) |

|||

| Line 38: | Line 38: | ||

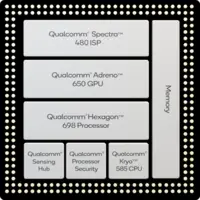

'''Snapdragon 865''' is a high-performance {{arch|64}} [[ARM]] [[system on a chip]] designed by [[Qualcomm]] and introduced in late [[2019]]. Fabricated on TSMC's [[7nm process]] ([[N7P]]), the 865 features four [[Kryo 585 Silver]] high-efficiency cores operating at 1.8 GHz along with three high-performance [[Kryo 585 Gold]] operating at 2.42 GHz and another prime [[Kryo 585 Gold]] core operating at 2.84 GHz. The Snapdragon 865 integrates the {{qualcomm|Adreno 650}} [[GPU]] operation at 600 MHz and supports up to 16 GiB of quad-channel LPDDR5-5500 memory. | '''Snapdragon 865''' is a high-performance {{arch|64}} [[ARM]] [[system on a chip]] designed by [[Qualcomm]] and introduced in late [[2019]]. Fabricated on TSMC's [[7nm process]] ([[N7P]]), the 865 features four [[Kryo 585 Silver]] high-efficiency cores operating at 1.8 GHz along with three high-performance [[Kryo 585 Gold]] operating at 2.42 GHz and another prime [[Kryo 585 Gold]] core operating at 2.84 GHz. The Snapdragon 865 integrates the {{qualcomm|Adreno 650}} [[GPU]] operation at 600 MHz and supports up to 16 GiB of quad-channel LPDDR5-5500 memory. | ||

| − | + | The Snapdragon 865 is designed to be paired with Qualcomm's X50 5G modem (an external chip) and an RF front-end interface chip (RFFE) to bring 5G NR, sub-6 GHz and mmWave, support. | |

| + | |||

| + | == Cache == | ||

| + | {{main|arm_holdings/microarchitectures/cortex-a77#Memory_Hierarchy|arm_holdings/microarchitectures/cortex-a55#Memory_Hierarchy|l1=Cortex-A77 § Cache|l2=Cortex-A55 § Cache}} | ||

| + | |||

| + | Prime {{armh|Cortex-A77|l=arch}}: | ||

| + | {{cache size | ||

| + | |l1 cache=128 KiB | ||

| + | |l1i cache=64 KiB | ||

| + | |l1i break=1x64 KiB | ||

| + | |l1i desc=4-way set associative | ||

| + | |l1d cache=64 KiB | ||

| + | |l1d break=1x64 KiB | ||

| + | |l1d desc=4-way set associative | ||

| + | |l2 cache=512 KiB | ||

| + | |l2 break=1x512 KiB | ||

| + | |l2 desc=8-way set associative | ||

| + | }} | ||

| + | |||

| + | 3 core cluster {{armh|Cortex-A77|l=arch}}: | ||

| + | {{cache size | ||

| + | |l1 cache=384 KiB | ||

| + | |l1i cache=192 KiB | ||

| + | |l1i break=3x64 KiB | ||

| + | |l1i desc=4-way set associative | ||

| + | |l1d cache=192 KiB | ||

| + | |l1d break=3x64 KiB | ||

| + | |l1d desc=4-way set associative | ||

| + | |l2 cache=768 KiB | ||

| + | |l2 break=3x256 KiB | ||

| + | |l2 desc=8-way set associative | ||

| + | }} | ||

| + | |||

| + | Quad-core cluster {{armh|Cortex-A55|l=arch}}: | ||

| + | {{cache size | ||

| + | |l1 cache=512 KiB | ||

| + | |l1i cache=256 KiB | ||

| + | |l1i break=4x64 KiB | ||

| + | |l1i desc=2-way set associative | ||

| + | |l1d cache=256 KiB | ||

| + | |l1d break=4x64 KiB | ||

| + | |l1d desc=4-way set associative | ||

| + | |l2 cache=512 KiB | ||

| + | |l2 break=4x128 KiB | ||

| + | |l2 desc=8-way set associative | ||

| + | }} | ||

| + | |||

| + | * 4 MiB L3 | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=LPDDR5-5500 | ||

| + | |type=LPDDR4X-4266 | ||

| + | |ecc=No | ||

| + | |max mem=16 GiB | ||

| + | |controllers=1 | ||

| + | |channels=4 | ||

| + | |width=16 bit | ||

| + | |max bandwidth=40.98 GiB/s | ||

| + | |frequency=2750 MHz | ||

| + | |bandwidth schan=10.24 GiB/s | ||

| + | |bandwidth dchan=20.49 GiB/s | ||

| + | |bandwidth qchan=40.98 GiB/s | ||

| + | }} | ||

| + | |||

| + | == DSP == | ||

| + | {{#set: dsp|Hexagon 698 DSP}} | ||

| + | This chip features [[Qualcomm]]'s {{qualcomm|Hexagon}} {{qualcomm|Hexagon 698|698}} DSP. | ||

| + | |||

| + | == Graphics == | ||

| + | {{integrated graphics | ||

| + | | gpu = Adreno 650 GPU | ||

| + | | designer = Qualcomm | ||

| + | | execution units = | ||

| + | | max displays = 2 | ||

| + | | max memory = | ||

| + | | frequency = 250 MHz | ||

| + | | max frequency = 600 MHz | ||

| + | |||

| + | | output crt = | ||

| + | | output sdvo = | ||

| + | | output dsi = | ||

| + | | output edp = | ||

| + | | output dp = | ||

| + | | output hdmi = | ||

| + | | output vga = | ||

| + | | output dvi = | ||

| + | |||

| + | | directx ver = 12 | ||

| + | | opengl ver = | ||

| + | | opengl es ver = 3.2 | ||

| + | | opencl ver = 2.0 | ||

| + | | vulkan ver = 1.1 | ||

| + | | hdmi ver = | ||

| + | | dp ver = | ||

| + | | edp ver = | ||

| + | | max res hdmi = | ||

| + | | max res hdmi freq = | ||

| + | | max res dp = | ||

| + | | max res dp freq = | ||

| + | | max res edp = | ||

| + | | max res edp freq = | ||

| + | | max res vga = | ||

| + | | max res vga freq = | ||

| + | }} | ||

| + | |||

| + | * Codec: H.265 (HEVC), H.264 (AVC), HDR10, HDR10+, HLG, VP8, VP9 | ||

| + | * HDR Playback Codec support for HDR10+, HDR10, HLG and Dolby Vision | ||

| + | * Volumetric VR video playback | ||

| + | * 8K 360 VR video playback | ||

| + | |||

| + | == Camera == | ||

| + | * ISP | ||

| + | ** Qualcomm Spectra 480 image signal processor | ||

| + | *** Dual 14-bit CV-ISPs | ||

| + | *** Hardware accelerator for computer vision (CV-ISP) | ||

| + | ** ZSL | ||

| + | *** Up to 30 MP dual camera | ||

| + | *** Up to 64 MP single camera | ||

| + | ** 200 MP Single | ||

| + | |||

| + | * Photo Capture: HEIF photo capture | ||

| + | * Video Capture: | ||

| + | ** Dolby Vision, HDR10, HDR10+, HEVC | ||

| + | ** 4K video capture with simultaneous 64 MP photo capture | ||

| + | ** Rec. 2020 color gamut video capture | ||

| + | ** Up to 10-bit color depth video capture | ||

| + | ** Slow motion video capture up to 720p at 960fps, HEVC Video Capture | ||

| + | |||

| + | == Connectivity == | ||

| + | * From the FastConnect 6800 Module | ||

| + | ** Wi-Fi | ||

| + | *** Standards: 802.11ax, 802.11ac wave 2, 802.11a/b/g, 802.11n | ||

| + | *** Bands: 2.4 GHz, 5 GHz | ||

| + | *** Peak Speed: 1.774 Gbps | ||

| + | *** 1024 QAM, 8x8 Sounding, MU-MIMO, Dual-band simultaneous (DBS), OFDMA, Target Wake-up Time (TWT) | ||

| + | ** Bluetooth | ||

| + | *** Bluetooth 5.1 | ||

| + | |||

| + | == Location == | ||

| + | * Systems: GPS, GLONASS, Beidou, Galileo, QZSS, SBAS, Dual frequency GNSS | ||

| + | |||

| + | == Utilizing devices == | ||

| + | <!-- | ||

| + | * [[used by::PHONE_HERE]] | ||

| + | --> | ||

| + | {{expand list}} | ||

| + | |||

| + | == Documents == | ||

| + | * [[:File:File:qualcomm-snapdragon-865-5g-mobile-platform-product-brief.pdf]] | ||

| + | |Product Brief]] | ||

Revision as of 16:48, 29 December 2019

| Edit Values | |

| Snapdragon 865 | |

| |

| General Info | |

| Designer | Qualcomm, ARM Holdings |

| Manufacturer | TSMC |

| Model Number | SDM865 |

| Part Number | SM8250 |

| Market | Mobile |

| Introduction | December 4, 2019 (announced) March, 2020 (launched) |

| General Specs | |

| Family | Snapdragon 800 |

| Series | 800 |

| Frequency | 1,800 MHz, 2,420 MHz, 2,840 MHz |

| Microarchitecture | |

| ISA | ARMv8 (ARM) |

| Microarchitecture | Cortex-A77, Cortex-A55 |

| Core Name | Kryo 585 Gold, Kryo 585 Silver |

| Process | 7 nm |

| Technology | CMOS |

| Word Size | 64 bit |

| Cores | 8 |

| Threads | 8 |

| Max Memory | 16 GiB |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Packaging | |

| |

| Succession | |

Snapdragon 865 is a high-performance 64-bit ARM system on a chip designed by Qualcomm and introduced in late 2019. Fabricated on TSMC's 7nm process (N7P), the 865 features four Kryo 585 Silver high-efficiency cores operating at 1.8 GHz along with three high-performance Kryo 585 Gold operating at 2.42 GHz and another prime Kryo 585 Gold core operating at 2.84 GHz. The Snapdragon 865 integrates the Adreno 650 GPU operation at 600 MHz and supports up to 16 GiB of quad-channel LPDDR5-5500 memory.

The Snapdragon 865 is designed to be paired with Qualcomm's X50 5G modem (an external chip) and an RF front-end interface chip (RFFE) to bring 5G NR, sub-6 GHz and mmWave, support.

Contents

Cache

- Main articles: Cortex-A77 § Cache and Cortex-A55 § Cache

Prime Cortex-A77:

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

3 core cluster Cortex-A77:

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Quad-core cluster Cortex-A55:

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

- 4 MiB L3

Memory controller

|

Integrated Memory Controller

|

||||||||||||||||||

|

||||||||||||||||||

DSP

This chip features Qualcomm's Hexagon 698 DSP.

Graphics

|

Integrated Graphics Information

|

||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||

- Codec: H.265 (HEVC), H.264 (AVC), HDR10, HDR10+, HLG, VP8, VP9

- HDR Playback Codec support for HDR10+, HDR10, HLG and Dolby Vision

- Volumetric VR video playback

- 8K 360 VR video playback

Camera

- ISP

- Qualcomm Spectra 480 image signal processor

- Dual 14-bit CV-ISPs

- Hardware accelerator for computer vision (CV-ISP)

- ZSL

- Up to 30 MP dual camera

- Up to 64 MP single camera

- 200 MP Single

- Qualcomm Spectra 480 image signal processor

- Photo Capture: HEIF photo capture

- Video Capture:

- Dolby Vision, HDR10, HDR10+, HEVC

- 4K video capture with simultaneous 64 MP photo capture

- Rec. 2020 color gamut video capture

- Up to 10-bit color depth video capture

- Slow motion video capture up to 720p at 960fps, HEVC Video Capture

Connectivity

- From the FastConnect 6800 Module

- Wi-Fi

- Standards: 802.11ax, 802.11ac wave 2, 802.11a/b/g, 802.11n

- Bands: 2.4 GHz, 5 GHz

- Peak Speed: 1.774 Gbps

- 1024 QAM, 8x8 Sounding, MU-MIMO, Dual-band simultaneous (DBS), OFDMA, Target Wake-up Time (TWT)

- Bluetooth

- Bluetooth 5.1

- Wi-Fi

Location

- Systems: GPS, GLONASS, Beidou, Galileo, QZSS, SBAS, Dual frequency GNSS

Utilizing devices

This list is incomplete; you can help by expanding it.

Documents

|Product Brief]]

- Pages using duplicate arguments in template calls

- all microprocessor models

- microprocessor models by qualcomm

- microprocessor models by qualcomm based on cortex-a77

- microprocessor models by qualcomm based on cortex-a55

- microprocessor models by arm holdings

- microprocessor models by arm holdings based on cortex-a77

- microprocessor models by arm holdings based on cortex-a55

- microprocessor models by tsmc

| back image |  + + |

| base frequency | 1,800 MHz (1.8 GHz, 1,800,000 kHz) +, 2,420 MHz (2.42 GHz, 2,420,000 kHz) + and 2,840 MHz (2.84 GHz, 2,840,000 kHz) + |

| core count | 8 + |

| core name | Kryo 585 Gold + and Kryo 585 Silver + |

| designer | Qualcomm + and ARM Holdings + |

| dsp | Hexagon 698 DSP + |

| family | Snapdragon 800 + |

| first announced | December 4, 2019 + |

| first launched | March 2020 + |

| full page name | qualcomm/snapdragon 800/865 + |

| has ecc memory support | false + |

| instance of | microprocessor + |

| integrated gpu | Adreno 650 GPU + |

| integrated gpu base frequency | 250 MHz (0.25 GHz, 250,000 KHz) + |

| integrated gpu designer | Qualcomm + |

| integrated gpu max frequency | 600 MHz (0.6 GHz, 600,000 KHz) + |

| isa | ARMv8 + |

| isa family | ARM + |

| l1$ size | 128 KiB (131,072 B, 0.125 MiB) +, 384 KiB (393,216 B, 0.375 MiB) + and 512 KiB (524,288 B, 0.5 MiB) + |

| l1d$ description | 4-way set associative + |

| l1d$ size | 64 KiB (65,536 B, 0.0625 MiB) +, 192 KiB (196,608 B, 0.188 MiB) + and 256 KiB (262,144 B, 0.25 MiB) + |

| l1i$ description | 4-way set associative + and 2-way set associative + |

| l1i$ size | 64 KiB (65,536 B, 0.0625 MiB) +, 192 KiB (196,608 B, 0.188 MiB) + and 256 KiB (262,144 B, 0.25 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + and 0.75 MiB (768 KiB, 786,432 B, 7.324219e-4 GiB) + |

| ldate | March 2020 + |

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Mobile + |

| max cpu count | 1 + |

| max memory | 16,384 MiB (16,777,216 KiB, 17,179,869,184 B, 16 GiB, 0.0156 TiB) + |

| max memory bandwidth | 40.98 GiB/s (41,963.52 MiB/s, 44.002 GB/s, 44,001.94 MB/s, 0.04 TiB/s, 0.044 TB/s) + |

| max memory channels | 4 + |

| microarchitecture | Cortex-A77 + and Cortex-A55 + |

| model number | SDM865 + |

| name | Snapdragon 865 + |

| part number | SM8250 + |

| process | 7 nm (0.007 μm, 7.0e-6 mm) + |

| series | 800 + |

| smp max ways | 1 + |

| supported memory type | LPDDR4X-4266 + |

| technology | CMOS + |

| thread count | 8 + |

| word size | 64 bit (8 octets, 16 nibbles) + |