From WikiChip

Difference between revisions of "amd/packages/socket sp3"

(Added a pin map.) |

|||

| Line 24: | Line 24: | ||

== Overview == | == Overview == | ||

SP3 is a socket specifically designed by AMD for their {{amd|EPYC}} family of server processors and is supported by processors based on the {{amd|Zen|l=arch}} microarchitectures. Physically, the package is identical to the one used for {{amd|Socket TR4}} for their {{amd|Threadripper}} processors, however, the features are very different. | SP3 is a socket specifically designed by AMD for their {{amd|EPYC}} family of server processors and is supported by processors based on the {{amd|Zen|l=arch}} microarchitectures. Physically, the package is identical to the one used for {{amd|Socket TR4}} for their {{amd|Threadripper}} processors, however, the features are very different. | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

== Supported Processors == | == Supported Processors == | ||

| Line 50: | Line 42: | ||

|class=sortable wikitable smwtable | |class=sortable wikitable smwtable | ||

}} | }} | ||

| + | |||

| + | == Package Photographs == | ||

| + | <gallery widths=500px heights=400px> | ||

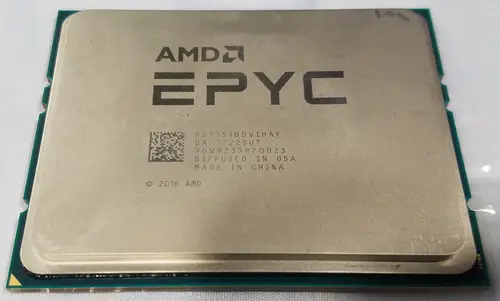

| + | File:amd naples (front).png|FCLGA-4094, package front | ||

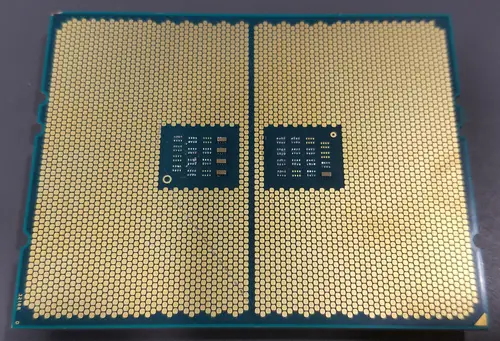

| + | File:amd naples (back).png|FCLGA-4094, package back | ||

| + | </gallery> | ||

| + | |||

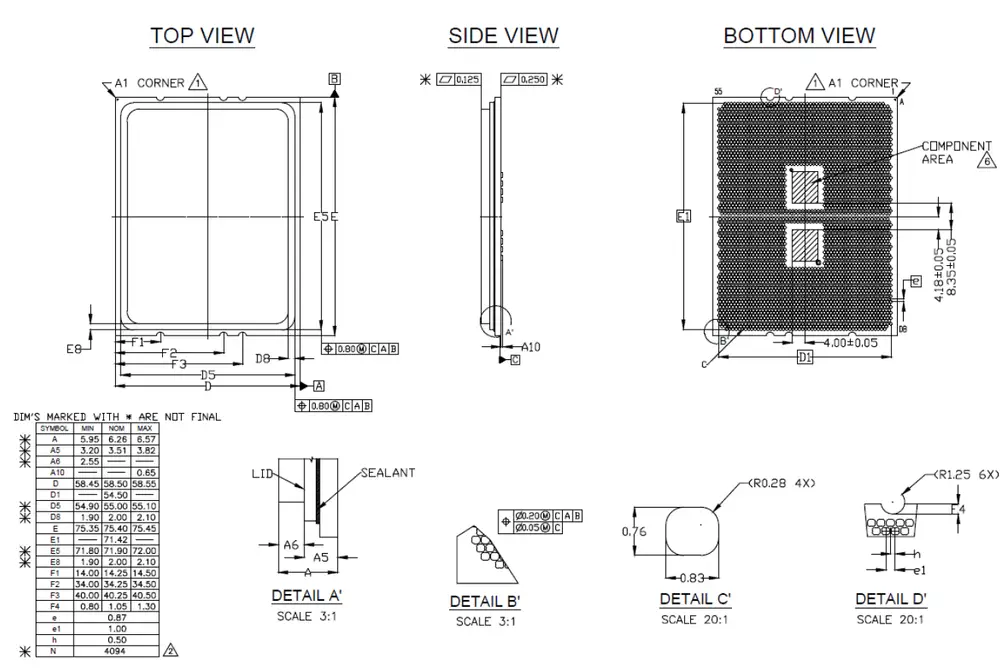

| + | == Package Diagram == | ||

| + | :[[File:sp3-details.png|1000px]] | ||

| + | |||

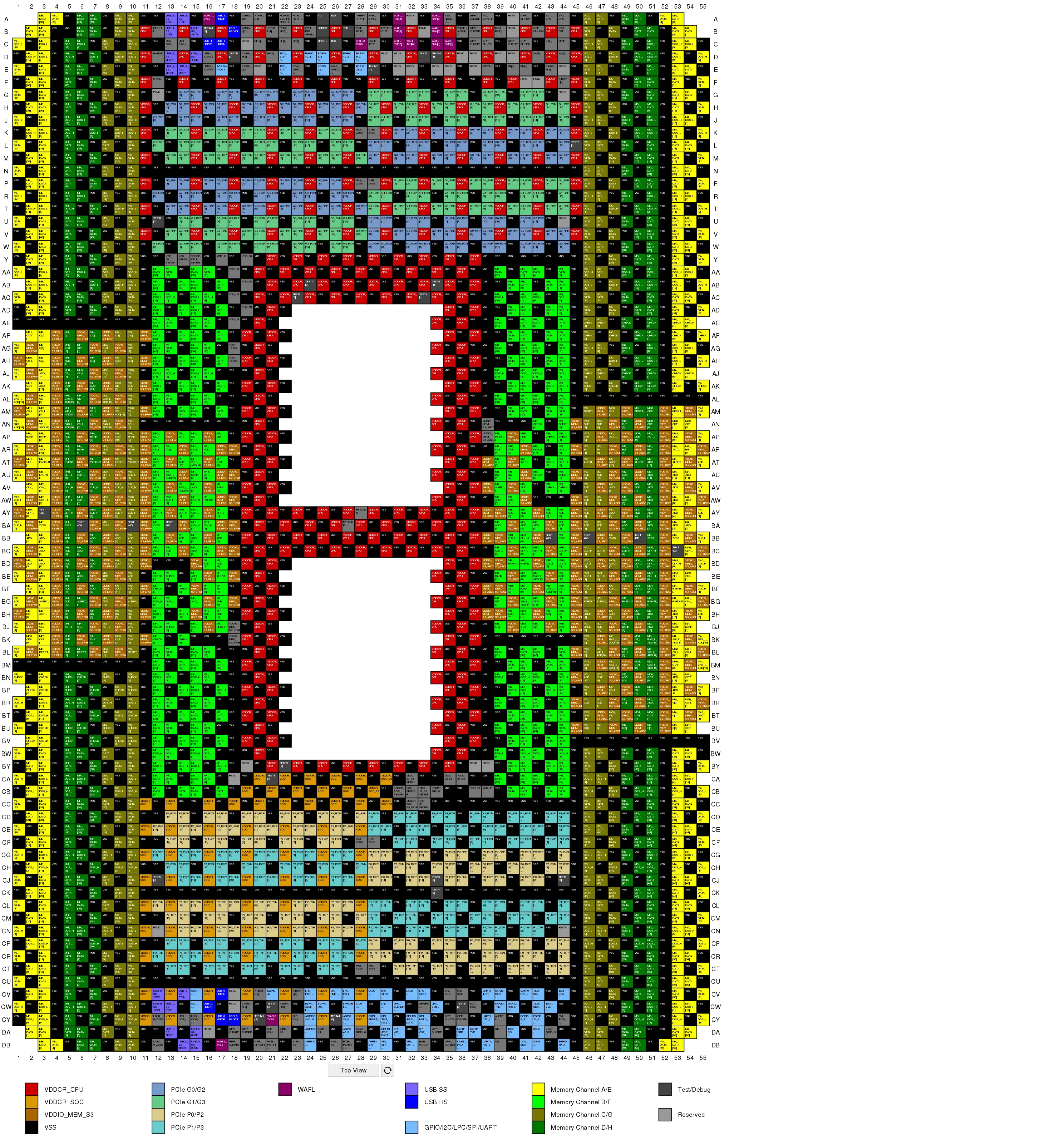

| + | == Pin Map == | ||

| + | :[[File:Socket SP3 pinmap.svg]] | ||

== Bibliography == | == Bibliography == | ||

* David. S. (March 2018). "[https://fuse.wikichip.org/news/1064/isscc-2018-amds-zeppelin-multi-chip-routing-and-packaging/ ISSCC 2018: AMD’s Zeppelin; Multi-chip routing and packaging]" | * David. S. (March 2018). "[https://fuse.wikichip.org/news/1064/isscc-2018-amds-zeppelin-multi-chip-routing-and-packaging/ ISSCC 2018: AMD’s Zeppelin; Multi-chip routing and packaging]" | ||

| − | * | + | * "Thermal Design Guide for Socket SP3 Processors", AMD Publ. #55423, Rev. 3.00, November 2017 |

| + | |||

| + | == See also == | ||

| + | * {{\\|Socket AM4}} | ||

| + | * {{\\|Socket TR4}} | ||

| + | * {{\\|Socket TRX4}} | ||

| + | |||

| + | [[Category:amd]] | ||

Revision as of 15:34, 19 July 2020

| Edit Values | |

| Socket SP3 | |

| General Info | |

| Designer | AMD |

| Introduction | May 16, 2017 (announced) June 20, 2017 (launched) |

| Market | Server |

| Microarchitecture | Zen |

| TDP | 120 W 120,000 mW , 155 W0.161 hp 0.12 kW 155,000 mW , 180 W0.208 hp 0.155 kW 180,000 mW 0.241 hp 0.18 kW |

| Package | |

| Name | FCLGA-4094 |

| Type | Organic Flip-Chip Land Grid Array |

| Contacts | 4094 |

| Dimension | 58.5 mm 5.85 cm × 75.4 mm2.303 in 7.54 cm 2.969 in |

| Pitch | 1.00 mm 0.0394 in |

| Socket | |

| Name | Socket SP3, LGA-4094 |

| Type | LGA |

Socket SP3 is a land grid array microprocessor socket designed by AMD for their EPYC family supported by the Zen microarchitectures. This socket is designed for ICs with a 4094-contact FCLGA packages.

Contents

Overview

SP3 is a socket specifically designed by AMD for their EPYC family of server processors and is supported by processors based on the Zen microarchitectures. Physically, the package is identical to the one used for Socket TR4 for their Threadripper processors, however, the features are very different.

Supported Processors

Package Photographs

Package Diagram

Pin Map

Bibliography

- David. S. (March 2018). "ISSCC 2018: AMD’s Zeppelin; Multi-chip routing and packaging"

- "Thermal Design Guide for Socket SP3 Processors", AMD Publ. #55423, Rev. 3.00, November 2017

See also

Facts about "Socket SP3 - Packages - AMD"

| designer | AMD + |

| first announced | May 16, 2017 + |

| first launched | June 20, 2017 + |

| instance of | package + |

| market segment | Server + |

| microarchitecture | Zen + |

| name | Socket SP3 + |

| package | FCLGA-4094 + |

| package contacts | 4,094 + |

| package length | 58.5 mm (5.85 cm, 2.303 in) + |

| package pitch | 1 mm (0.0394 in) + |

| package type | Organic Flip-Chip Land Grid Array + |

| package width | 75.4 mm (7.54 cm, 2.969 in) + |

| socket | Socket SP3 + and LGA-4094 + |

| tdp | 120 W (120,000 mW, 0.161 hp, 0.12 kW) +, 155 W (155,000 mW, 0.208 hp, 0.155 kW) + and 180 W (180,000 mW, 0.241 hp, 0.18 kW) + |