From WikiChip

Difference between revisions of "fujitsu/sparc64/sparc64 xii"

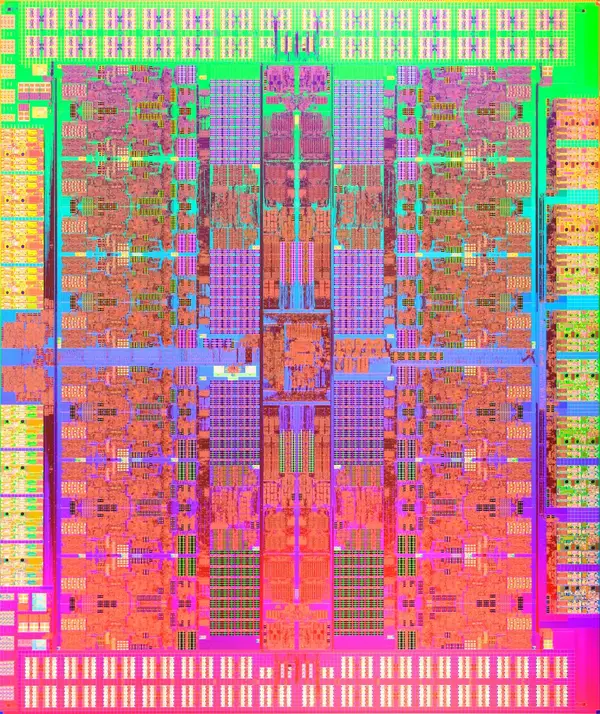

(→Die Shot) |

|||

| Line 103: | Line 103: | ||

| socket 1 type = | | socket 1 type = | ||

}} | }} | ||

| + | [[File:sparc64 xii wafer.jpg|right|thumb|XII Wafer]] | ||

'''SPARC64 XII''' is a high-performance {{arch|64}} [[dodeca-core]] [[SPARC]] microprocessor designed by [[Fujitsu]] and introduced in April [[2017]]. | '''SPARC64 XII''' is a high-performance {{arch|64}} [[dodeca-core]] [[SPARC]] microprocessor designed by [[Fujitsu]] and introduced in April [[2017]]. | ||

Revision as of 22:39, 12 April 2017

SPARC64 XII is a high-performance 64-bit dodeca-core SPARC microprocessor designed by Fujitsu and introduced in April 2017.

Cache

| This section is empty; you can help add the missing info by editing this page. |

Expansions

| This section is empty; you can help add the missing info by editing this page. |

Die Shot

Facts about "SPARC64 XII - Fujitsu"

| base frequency | 4,250 MHz (4.25 GHz, 4,250,000 kHz) + |

| core count | 12 + |

| designer | Fujitsu + |

| family | SPARC64 + |

| first announced | 2015 + |

| first launched | April 4, 2017 + |

| full page name | fujitsu/sparc64/sparc64 xii + |

| instance of | microprocessor + |

| isa | SPARC V9 + |

| isa family | SPARC + |

| ldate | April 4, 2017 + |

| main image |  + + |

| main image caption | SPARC64 XII Chip + |

| manufacturer | TSMC + |

| market segment | Server + |

| max cpu count | 32 + |

| max memory | 2,097,152 MiB (2,147,483,648 KiB, 2,199,023,255,552 B, 2,048 GiB, 2 TiB) + |

| microarchitecture | SPARC64 XII + |

| model number | SPARC64 XII + |

| name | SPARC64 XII + |

| process | 20 nm (0.02 μm, 2.0e-5 mm) + |

| smp max ways | 32 + |

| technology | CMOS + |

| thread count | 96 + |

| word size | 64 bit (8 octets, 16 nibbles) + |