m (At32Hz moved page intel/silvermont to intel/microarchitectures/silvermont) |

|

(No difference)

| |

Revision as of 13:24, 9 April 2016

Silvermont is Intel's 22 nm microarchitecture for the Atom family of system on chips. Introduced in 2013, Silvermont was the successor to Saltwell, targeting smartphones, tablets, embedded devices, and consumer electronics.

Contents

Codenames

| Platform | Core | Target |

|---|---|---|

| Merrifield | Tangier | Smartphones |

| Bay Trail | Valleyview | Tablets |

| Edisonville | Avoton | Microservers |

| Edisonville | Rangeley | Embedded Networking |

Architecture

Silvermont introduced a number of significant changes from the previous Atom microarchitecture in addition to the increase performance and lower power consumption.

Key changes from Saltwell

- Pipeline is now OoOE

- 14 stage (2 shorter)

- 10 stage panelty for miss (3 shorter)

- Support up to Westmere

- Multi-core modular system (up to 8 cores)

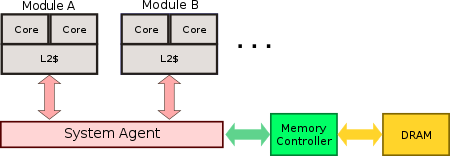

Core Modules

Silvermont employees a modular core design. Each module consists of 2 cores and 2 threads with exclusive hardware - resources are not shared. Within each module is a 1 MB L2 cache shared between the two cores. The L1 is still identical to Saltwell's: 32K L1I$ and 24K L1D$. Each module as a dedicated point-to-point interface (IDI) to the system agent. Each module has a per-core frequency and power management support. This is a departure from previous microarchitectures as well as similar desktop (e.g. Core) where all cores are tied to the same frequency.

System Agent

The system agent acts very much like a northbridge however it does a much better job than previous Atom microarchitectures performance-wise because it's capable of reordering all requests from all consumers (e.g. Core, GPU).

Memory Hierarchy

- Cache

- Hardware prefetchers

- L1 Cache:

- 32 KB 8-way set associative instruction

- 1 read and 1 write port

- 24 KB 6-way set associative data

- 1 read and 1 write port

- 8 transistors (instead of 6) to reduce voltage

- Per core

- 32 KB 8-way set associative instruction

- L2 Cache:

- 512 KB 8-way set associative

- ECC

- separate voltage rail, fixed @ 1.05V

- Per core

- L3 Cache:

- No level 3 cache

- Non-Cache Shared State Memory

- 256KB low-power SRAM

- separate voltage plane

- always-on block that stores architectural states while in various power saving modes

- RAM

- Maximum of 1GB, 2 GB, and 4 GB

- dual 32-bit channels, 1 or 2 ranks per channel

| codename | Silvermont + |

| core count | 1 +, 2 +, 4 + and 8 + |

| designer | Intel + |

| first launched | 2013 + |

| full page name | intel/microarchitectures/silvermont + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Silvermont + |

| phase-out | 2015 + |

| pipeline stages (max) | 14 + |

| pipeline stages (min) | 12 + |

| process | 22 nm (0.022 μm, 2.2e-5 mm) + |