From WikiChip

Difference between revisions of "hisilicon/hydra"

| (One intermediate revision by the same user not shown) | |||

| Line 1: | Line 1: | ||

{{hisilicon title|Hydra}}{{interconnect arch}} | {{hisilicon title|Hydra}}{{interconnect arch}} | ||

| − | '''Hydra''' or '''Hydra Interface''' | + | '''Hydra''' or '''Hydra Interface''' is a custom interface designed by [[HiSilicon]] for their {{hisilicon|Kunpeng}} ({{hisilicon|Hi16xx}}) family of [[ARM]] server processors designed to facilitate coherent [[symmetric multiprocessing]] support. |

== Overview == | == Overview == | ||

| Line 16: | Line 16: | ||

| 2 || 2x8 || 20 GB/s || 24 GB/s | | 2 || 2x8 || 20 GB/s || 24 GB/s | ||

|- | |- | ||

| − | | 3 || 3x8 || 30 | + | | 3 || 3x8 || 30 GB/s || 36 GB/s |

|} | |} | ||

Latest revision as of 19:51, 5 May 2019

| Interconnect Architectures | |

| |

| Concepts | |

| General | |

| Peripheral | |

| Storage Devices | |

| Audio Devices | |

Hydra or Hydra Interface is a custom interface designed by HiSilicon for their Kunpeng (Hi16xx) family of ARM server processors designed to facilitate coherent symmetric multiprocessing support.

Overview[edit]

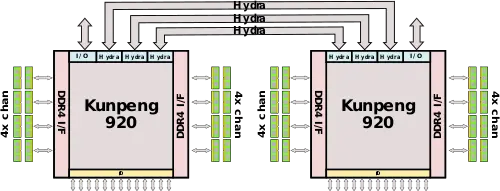

The Hydra Interface is a high-speed cache coherent interconnect architecture designed to facilitate symmetric multiprocessing between their Kunpeng processors. The Hydra interface is multiplexed over a number of extra PCIe lanes. Each Hydra interface has either x4 or 8x lanes.

When in 2-way SMP, multiple Hydra interfaces are combined.

| 2-way SMP Hydra Interface | |||

|---|---|---|---|

| Links | 10 GT/s | 12 GT/s | |

| 1 | 1x8 | 10 GB/s | 12 GB/s |

| 2 | 2x8 | 20 GB/s | 24 GB/s |

| 3 | 3x8 | 30 GB/s | 36 GB/s |

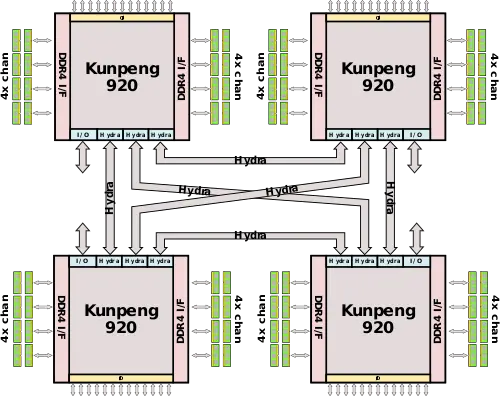

In a 4-way SMP, three Hydra interfaces are used per CPU with one link between each CPU, creating an all-to-all connection.