| Interconnect Architectures | |

| |

| Concepts | |

| |

| General | |

| Peripheral | |

| Storage Devices | |

| Audio Devices | |

Low-voltage-In-Package-INterCONnect (LIPINCON) is a proprietary system interconnect architecture that facilitates data transmission across all linked components.

Overview[edit]

LIPINCON is an interconnect architecture designed for chiplet designs with advanced packaging technologies such as InFO and CoWoS. LIPINCON uses a timing compensation mechanism in order to achieve a low-power and small area slave PHY (e.g., memory die or a transceiver die) while excluding the PLL/DLL but retaining good timing margins.

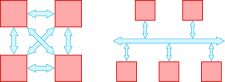

Architecture[edit]

The architecture is designed to take advantage of an advanced packaging technology such as CoWoS whereby multiple dies are stacked on a silicon interposer communicating by PHYs over short wires. LIPINCON uses two different types of PHYs: PHYC for an SoC die and PHYM for a memory, transceiver, or similar kind of dies. The clock source in the PHYM relies on one system clock propagated from PHYC. There is no PLL/DLL function blocks built in PHYM because it assumes that the SoC will generally be fabricated on a more advanced node and is therefore capable of handling this more efficiently than a memory/transceiver that may be made on a more mature node.

Bibliography[edit]

- TSMC, MS Lin et a., 2013 VLSI Symposium