(6138p) |

|||

| (9 intermediate revisions by 2 users not shown) | |||

| Line 13: | Line 13: | ||

|release price=$4937 | |release price=$4937 | ||

|family=Xeon Gold | |family=Xeon Gold | ||

| − | |series= | + | |series=6100 |

|locked=Yes | |locked=Yes | ||

|frequency=2,000 MHz | |frequency=2,000 MHz | ||

| Line 32: | Line 32: | ||

|process=14 nm | |process=14 nm | ||

|technology=CMOS | |technology=CMOS | ||

| + | |mcp=Yes | ||

| + | |die count=2 | ||

|word size=64 bit | |word size=64 bit | ||

|core count=20 | |core count=20 | ||

| Line 42: | Line 44: | ||

|dts min=0 °C | |dts min=0 °C | ||

|dts max=93 °C | |dts max=93 °C | ||

| − | |package | + | |package name 1=intel,fclga_3647 |

}} | }} | ||

| − | '''Xeon Gold 6138P''' is a {{arch|64}} [[20-core]] [[x86]] multi-socket high performance server microprocessor introduced by [[Intel]] in early-[[2018]]. This chip supports up to 2-way multiprocessing. The Gold 6138P, which is based on the server configuration of the {{intel|Skylake (server)|Skylake|l=arch}} microarchitecture and is manufactured on a [[14 nm process|14 nm+ process]], sports 2 {{x86|AVX-512}} [[FMA]] units as well as | + | [[File:skylake-fpga (front, back).jpg|right|thumb|Package]] |

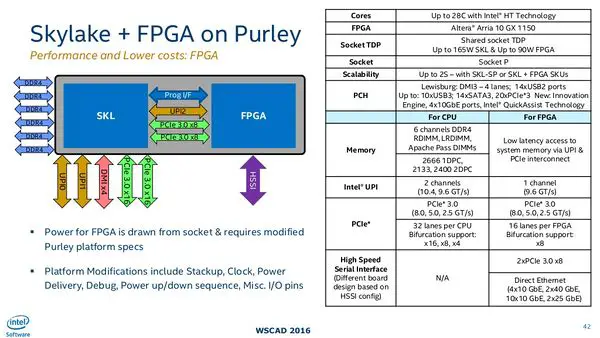

| + | '''Xeon Gold 6138P''' is a {{arch|64}} [[20-core]] [[x86]] multi-socket high performance server microprocessor introduced by [[Intel]] in early-[[2018]]. This chip supports up to 2-way multiprocessing. The Gold 6138P, which is based on the server configuration of the {{intel|Skylake (server)|Skylake|l=arch}} microarchitecture and is manufactured on a [[14 nm process|14 nm+ process]], sports 2 {{x86|AVX-512}} [[FMA]] units as well as two {{intel|Ultra Path Interconnect}} links. This microprocessor, which operates at 2 GHz with a TDP of 125 W and a {{intel|turbo boost}} frequency of up to 3.7 GHz, supports up 768 GiB of hexa-channel DDR4-2666 ECC memory. | ||

| + | |||

| + | This processor features an Arria 10 GX 1150 [[FPGA]] on-package, offering 1,150,000 [[logic elements]]. | ||

| + | |||

| + | == Overview == | ||

| + | The Xeon Gold 6138P is a special variant of the {{\\|6138}} with almost identical specs except for the TDP, maximum CPU support, and price. For this SKU, Intel is repurposing one of the three {{intel|UPI}} links from the CPU for the FPGA, providing the FPGA with a [[cache coherent]] link to the CPU. | ||

| + | |||

| + | === FPGA === | ||

| + | On the same package is an Arria 10 GX 1150 which comes with 1,150,000 [[logic elements]], 427,200 ALM (Intel's adaptive logic modules), and 1,708,800 registers. The FPGA incorporates a number of High-Speed Serial Interface (HSSI) ports which are exposed through the socket and may be used as: 4x 10 GbE KR ports, 2x 40 GbE ports (2x 40 GbE to gearbox or 2x 25 GbE), or 10x 10 GbE CAUI-10 ports. | ||

| + | |||

| + | |||

| + | :[[File:skylake-sp fpga overview.jpg|600px]] | ||

== Cache == | == Cache == | ||

Latest revision as of 01:14, 24 May 2019

| Edit Values | |

| Xeon Gold 6138P | |

| |

| General Info | |

| Designer | Intel |

| Manufacturer | Intel |

| Model Number | 6138P |

| Part Number | CM8067303824101 |

| S-Spec | SRCUG |

| Market | Server |

| Introduction | May 16, 2018 (announced) May 16, 2018 (launched) |

| Release Price | $4937 |

| Shop | Amazon |

| General Specs | |

| Family | Xeon Gold |

| Series | 6100 |

| Locked | Yes |

| Frequency | 2,000 MHz |

| Turbo Frequency | 3,700 MHz (1 core) |

| Bus type | DMI 3.0 |

| Bus rate | 4 × 8 GT/s |

| Clock multiplier | 20 |

| CPUID | 0x50654 |

| Microarchitecture | |

| ISA | x86-64 (x86) |

| Microarchitecture | Skylake (server) |

| Platform | Purley |

| Chipset | Lewisburg |

| Core Name | Skylake SP |

| Core Family | 6 |

| Core Stepping | H0 |

| Process | 14 nm |

| Technology | CMOS |

| MCP | Yes (2 dies) |

| Word Size | 64 bit |

| Cores | 20 |

| Threads | 40 |

| Max Memory | 768 GiB |

| Multiprocessing | |

| Max SMP | 2-Way (Multiprocessor) |

| Electrical | |

| TDP | 195 W |

| Tcase | 0 °C – 86 °C |

| TDTS | 0 °C – 93 °C |

| Packaging | |

| Package | FCLGA-3647 (FCLGA) |

| Dimension | 76.16 mm × 56.6 mm |

| Pitch | 0.8585 mm × 0.9906 mm |

| Contacts | 3647 |

| Socket | Socket P, LGA-3647 |

Xeon Gold 6138P is a 64-bit 20-core x86 multi-socket high performance server microprocessor introduced by Intel in early-2018. This chip supports up to 2-way multiprocessing. The Gold 6138P, which is based on the server configuration of the Skylake microarchitecture and is manufactured on a 14 nm+ process, sports 2 AVX-512 FMA units as well as two Ultra Path Interconnect links. This microprocessor, which operates at 2 GHz with a TDP of 125 W and a turbo boost frequency of up to 3.7 GHz, supports up 768 GiB of hexa-channel DDR4-2666 ECC memory.

This processor features an Arria 10 GX 1150 FPGA on-package, offering 1,150,000 logic elements.

Overview[edit]

The Xeon Gold 6138P is a special variant of the 6138 with almost identical specs except for the TDP, maximum CPU support, and price. For this SKU, Intel is repurposing one of the three UPI links from the CPU for the FPGA, providing the FPGA with a cache coherent link to the CPU.

FPGA[edit]

On the same package is an Arria 10 GX 1150 which comes with 1,150,000 logic elements, 427,200 ALM (Intel's adaptive logic modules), and 1,708,800 registers. The FPGA incorporates a number of High-Speed Serial Interface (HSSI) ports which are exposed through the socket and may be used as: 4x 10 GbE KR ports, 2x 40 GbE ports (2x 40 GbE to gearbox or 2x 25 GbE), or 10x 10 GbE CAUI-10 ports.

Cache[edit]

- Main article: Skylake § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions[edit]

|

Expansion Options

|

||||||||

|

||||||||

Features[edit]

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Frequencies[edit]

- See also: Intel's CPU Frequency Behavior

| Mode | Base | Turbo Frequency/Active Cores | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | ||

| Normal | 2,000 MHz | 3,700 MHz | 3,700 MHz | 3,500 MHz | 3,500 MHz | 3,400 MHz | 3,400 MHz | 3,400 MHz | 3,400 MHz | 3,200 MHz | 3,200 MHz | 3,200 MHz | 3,200 MHz | 2,900 MHz | 2,900 MHz | 2,900 MHz | 2,900 MHz | 2,700 MHz | 2,700 MHz | 2,700 MHz | 2,700 MHz |

| AVX2 | 1,600 MHz | 3,600 MHz | 3,600 MHz | 3,400 MHz | 3,400 MHz | 3,200 MHz | 3,200 MHz | 3,200 MHz | 3,200 MHz | 2,700 MHz | 2,700 MHz | 2,700 MHz | 2,700 MHz | 2,500 MHz | 2,500 MHz | 2,500 MHz | 2,500 MHz | 2,300 MHz | 2,300 MHz | 2,300 MHz | 2,300 MHz |

| AVX512 | 1,300 MHz | 3,500 MHz | 3,500 MHz | 3,300 MHz | 3,300 MHz | 2,700 MHz | 2,700 MHz | 2,700 MHz | 2,700 MHz | 2,300 MHz | 2,300 MHz | 2,300 MHz | 2,300 MHz | 2,000 MHz | 2,000 MHz | 2,000 MHz | 2,000 MHz | 1,900 MHz | 1,900 MHz | 1,900 MHz | 1,900 MHz |

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Xeon Gold 6138P - Intel#io + |

| base frequency | 2,000 MHz (2 GHz, 2,000,000 kHz) + |

| bus links | 4 + |

| bus rate | 8,000 MT/s (8 GT/s, 8,000,000 kT/s) + |

| bus type | DMI 3.0 + |

| chipset | Lewisburg + |

| clock multiplier | 20 + |

| core count | 20 + |

| core family | 6 + |

| core name | Skylake SP + |

| core stepping | H0 + |

| cpuid | 0x50654 + |

| designer | Intel + |

| die count | 2 + |

| family | Xeon Gold + |

| first announced | May 16, 2018 + |

| first launched | May 16, 2018 + |

| full page name | intel/xeon gold/6138p + |

| has advanced vector extensions | true + |

| has advanced vector extensions 2 | true + |

| has advanced vector extensions 512 | true + |

| has ecc memory support | true + |

| has extended page tables support | true + |

| has feature | Advanced Vector Extensions +, Advanced Vector Extensions 2 +, Advanced Vector Extensions 512 +, Advanced Encryption Standard Instruction Set Extension +, Hyper-Threading Technology +, Turbo Boost Technology 2.0 +, Enhanced SpeedStep Technology +, Speed Shift Technology +, Trusted Execution Technology +, Intel vPro Technology +, Intel VT-x +, Intel VT-d +, Extended Page Tables + and Transactional Synchronization Extensions + |

| has intel enhanced speedstep technology | true + |

| has intel speed shift technology | true + |

| has intel trusted execution technology | true + |

| has intel turbo boost technology 2 0 | true + |

| has intel vpro technology | true + |

| has intel vt-d technology | true + |

| has intel vt-x technology | true + |

| has locked clock multiplier | true + |

| has second level address translation support | true + |

| has simultaneous multithreading | true + |

| has transactional synchronization extensions | true + |

| has x86 advanced encryption standard instruction set extension | true + |

| instance of | microprocessor + |

| is multi-chip package | true + |

| isa | x86-64 + |

| isa family | x86 + |

| l1$ size | 1,280 KiB (1,310,720 B, 1.25 MiB) + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 640 KiB (655,360 B, 0.625 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 640 KiB (655,360 B, 0.625 MiB) + |

| l2$ description | 16-way set associative + |

| l2$ size | 20 MiB (20,480 KiB, 20,971,520 B, 0.0195 GiB) + |

| l3$ description | 11-way set associative + |

| l3$ size | 27.5 MiB (28,160 KiB, 28,835,840 B, 0.0269 GiB) + |

| ldate | May 16, 2018 + |

| main image |  + + |

| manufacturer | Intel + |

| market segment | Server + |

| max case temperature | 359.15 K (86 °C, 186.8 °F, 646.47 °R) + |

| max cpu count | 2 + |

| max dts temperature | 93 °C + |

| max memory | 786,432 MiB (805,306,368 KiB, 824,633,720,832 B, 768 GiB, 0.75 TiB) + |

| max memory bandwidth | 119.21 GiB/s (122,071.04 MiB/s, 128.001 GB/s, 128,000.763 MB/s, 0.116 TiB/s, 0.128 TB/s) + |

| max memory channels | 6 + |

| max pcie lanes | 48 + |

| microarchitecture | Skylake (server) + |

| min case temperature | 273.15 K (0 °C, 32 °F, 491.67 °R) + |

| min dts temperature | 0 °C + |

| model number | 6138P + |

| name | Xeon Gold 6138P + |

| package | FCLGA-3647 + |

| part number | CM8067303824101 + |

| platform | Purley + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| release price | $ 4,937.00 (€ 4,443.30, £ 3,998.97, ¥ 510,140.21) + |

| s-spec | SRCUG + |

| series | 6100 + |

| smp max ways | 2 + |

| socket | Socket P + and LGA-3647 + |

| supported memory type | DDR4-2666 + |

| tdp | 195 W (195,000 mW, 0.261 hp, 0.195 kW) + |

| technology | CMOS + |

| thread count | 40 + |

| turbo frequency (1 core) | 3,700 MHz (3.7 GHz, 3,700,000 kHz) + |

| word size | 64 bit (8 octets, 16 nibbles) + |