From WikiChip

Difference between revisions of "loongson/godson 2/2e"

(Created page with "{{loongson title|Godson-2E}} {{mpu | name = Godson-2E | image = godson-2e.jpg | image size = 250px | caption = Godson-2E chip...") |

m (Bot: moving all {{mpu}} to {{chip}}) |

||

| (17 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{loongson title|Godson-2E}} | {{loongson title|Godson-2E}} | ||

| − | {{ | + | {{chip |

| name = Godson-2E | | name = Godson-2E | ||

| image = godson-2e.jpg | | image = godson-2e.jpg | ||

| Line 9: | Line 9: | ||

| model number = 2E | | model number = 2E | ||

| part number = CZ70 | | part number = CZ70 | ||

| − | | part number | + | | part number 2 = |

| market = Desktop | | market = Desktop | ||

| first announced = 2006 | | first announced = 2006 | ||

| Line 19: | Line 19: | ||

| family = Godson 2 | | family = Godson 2 | ||

| series = Godson 2 | | series = Godson 2 | ||

| − | | locked = | + | | locked = |

| frequency = 1,000 MHz | | frequency = 1,000 MHz | ||

| frequency 2 = | | frequency 2 = | ||

| frequency N = | | frequency N = | ||

| − | | bus type = | + | | bus type = SysAD |

| bus speed = <!-- (Property::bus speed) --> | | bus speed = <!-- (Property::bus speed) --> | ||

| bus rate = <!-- (Property::bus rate) --> | | bus rate = <!-- (Property::bus rate) --> | ||

| Line 31: | Line 31: | ||

| isa family = MIPS | | isa family = MIPS | ||

| isa = MIPS64 | | isa = MIPS64 | ||

| − | | microarch = | + | | microarch = GS464 |

| platform = | | platform = | ||

| chipset = | | chipset = | ||

| − | | core name = | + | | core name = GS464 |

| core family = | | core family = | ||

| core model = | | core model = | ||

| core stepping = | | core stepping = | ||

| process = 90 nm | | process = 90 nm | ||

| − | | transistors = | + | | transistors = 47,000,000 |

| technology = CMOS | | technology = CMOS | ||

| − | | die area = | + | | die area = 36 mm² |

| die width = | | die width = | ||

| die length = | | die length = | ||

| Line 50: | Line 50: | ||

| max memory = | | max memory = | ||

| − | + | ||

| power = 7 W | | power = 7 W | ||

| − | | v core = | + | | v core = 1.2 V |

| − | |||

| − | |||

| − | |||

| v io = | | v io = | ||

| v io tolerance = | | v io tolerance = | ||

| Line 89: | Line 86: | ||

| socket 0 type = | | socket 0 type = | ||

}} | }} | ||

| − | '''Godson-2E''' is a {{arch|64}} [[MIPS]] performance processor developed by [[Institute of Computing Technology of the Chinese Academy of Sciences|ICT]] and later [[Loongson]] for desktop computers. Introduced in early [[2006]], the Godson-2E operates at up to 1 GHz consuming 7W. This chip was manufactured on [[STMicroelectronics]]' [[90 nm process]] and provides roughly three times the performance of {{\\|2C}}. This processor is known as [[China]]'s first processor to reach gigahertz frequency. | + | '''Godson-2E''' ('''龙芯2E''') is a {{arch|64}} [[MIPS]] performance processor developed by [[Institute of Computing Technology of the Chinese Academy of Sciences|ICT]] and later [[Loongson]] for desktop computers. Introduced in early [[2006]], the Godson-2E operates at up to 1 GHz consuming 7W. This chip was manufactured on [[STMicroelectronics]]' [[90 nm process]] and provides roughly three times the performance of {{\\|2C}}. This processor is known as [[China]]'s first processor to reach gigahertz frequency. |

| + | |||

| + | The Godson-2E introduces a number of improvements over {{\\|2C|its predecessor}}, including double the clock frequency, the addition of a large [[L2 cache]], and the integration of the [[northbridge]] on-die, supporting up to DDR-333. | ||

| + | == Cache == | ||

| + | {{main|loongson/microarchitectures/GS464#Memory_Hierarchy|l1=GS464 § Cache}} | ||

| + | {{cache size | ||

| + | |l1 cache=128 KiB | ||

| + | |l1i cache=64 KiB | ||

| + | |l1i break=1x64 KiB | ||

| + | |l1i desc=4-way set associative | ||

| + | |l1d cache=64 KiB | ||

| + | |l1d break=1x64 KiB | ||

| + | |l1d desc=4-way set associative | ||

| + | |l1d policy= | ||

| + | |l2 cache=512 KiB | ||

| + | |l2 break=1x512 KiB | ||

| + | |l2 desc=4-way set associative | ||

| + | |l2 policy= | ||

| + | }} | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=DDR-333 | ||

| + | |ecc=Yes | ||

| + | |max mem=2 GiB | ||

| + | |controllers=1 | ||

| + | |channels=1 | ||

| + | |max bandwidth=4.967 GiB/s | ||

| + | |bandwidth schan=4.967 GiB/s | ||

| + | }} | ||

| + | |||

| + | == Graphics == | ||

| + | This chip had no [[integrated graphics processing unit]]. | ||

| + | |||

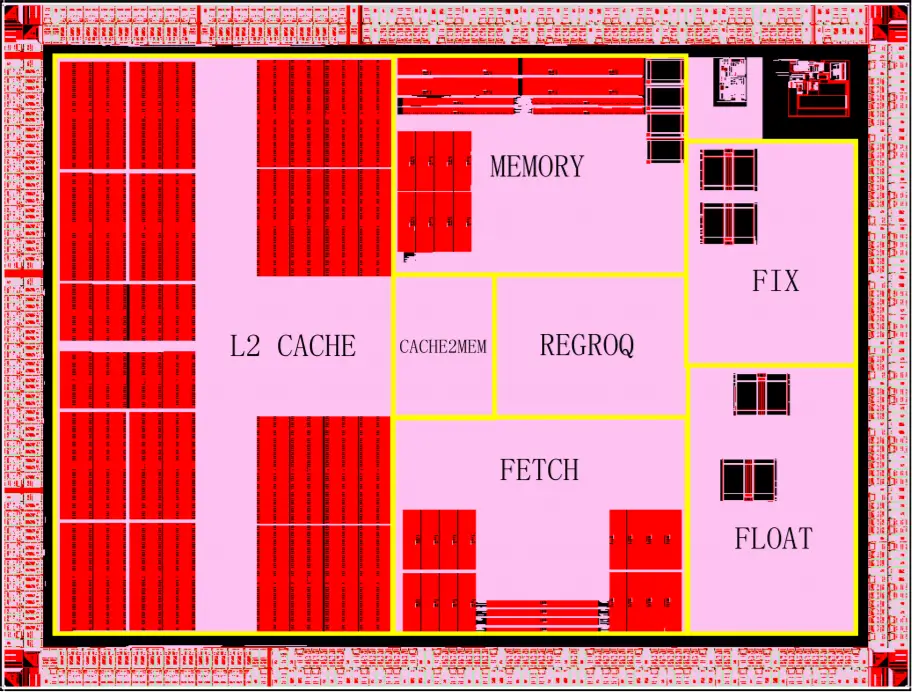

| + | == Die Shot == | ||

| + | * [[90 nm process]] | ||

| + | * 47,000,000 transistors | ||

| + | * 36 mm² | ||

| + | [[File:godson-2e die shot.png]] | ||

| + | |||

| + | == References == | ||

| + | * Hu, Wei-Wu, and Jian Wang. "Making effective decisions in computer architects’ real-world: Lessons and experiences with Godson-2 processor designs." Journal of Computer Science and Technology 23.4 (2008): 620-632. | ||

Latest revision as of 15:31, 13 December 2017

| Edit Values | |

| Godson-2E | |

| |

| Godson-2E chip | |

| General Info | |

| Designer | Loongson |

| Manufacturer | STMicroelectronics |

| Model Number | 2E |

| Part Number | CZ70 |

| Market | Desktop |

| Introduction | 2006 (announced) March 18, 2006 (launched) |

| General Specs | |

| Family | Godson 2 |

| Series | Godson 2 |

| Frequency | 1,000 MHz |

| Bus type | SysAD |

| Microarchitecture | |

| ISA | MIPS64 (MIPS) |

| Microarchitecture | GS464 |

| Core Name | GS464 |

| Process | 90 nm |

| Transistors | 47,000,000 |

| Technology | CMOS |

| Die | 36 mm² |

| Word Size | 64 bit |

| Cores | 1 |

| Threads | 1 |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| Power dissipation | 7 W |

| Vcore | 1.2 V |

Godson-2E (龙芯2E) is a 64-bit MIPS performance processor developed by ICT and later Loongson for desktop computers. Introduced in early 2006, the Godson-2E operates at up to 1 GHz consuming 7W. This chip was manufactured on STMicroelectronics' 90 nm process and provides roughly three times the performance of 2C. This processor is known as China's first processor to reach gigahertz frequency.

The Godson-2E introduces a number of improvements over its predecessor, including double the clock frequency, the addition of a large L2 cache, and the integration of the northbridge on-die, supporting up to DDR-333.

Cache[edit]

- Main article: GS464 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Graphics[edit]

This chip had no integrated graphics processing unit.

Die Shot[edit]

- 90 nm process

- 47,000,000 transistors

- 36 mm²

References[edit]

- Hu, Wei-Wu, and Jian Wang. "Making effective decisions in computer architects’ real-world: Lessons and experiences with Godson-2 processor designs." Journal of Computer Science and Technology 23.4 (2008): 620-632.

Facts about "Godson-2E - Loongson"

| base frequency | 1,000 MHz (1 GHz, 1,000,000 kHz) + |

| bus type | SysAD + |

| core count | 1 + |

| core name | GS464 + |

| core voltage | 1.2 V (12 dV, 120 cV, 1,200 mV) + |

| designer | Loongson + |

| die area | 36 mm² (0.0558 in², 0.36 cm², 36,000,000 µm²) + |

| family | Godson 2 + |

| first announced | 2006 + |

| first launched | March 18, 2006 + |

| full page name | loongson/godson 2/2e + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| isa | MIPS64 + |

| isa family | MIPS + |

| l1$ size | 128 KiB (131,072 B, 0.125 MiB) + |

| l1d$ description | 4-way set associative + |

| l1d$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l2$ description | 4-way set associative + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| ldate | March 18, 2006 + |

| main image |  + + |

| main image caption | Godson-2E chip + |

| manufacturer | STMicroelectronics + |

| market segment | Desktop + |

| max cpu count | 1 + |

| max memory bandwidth | 4.967 GiB/s (5,086.208 MiB/s, 5.333 GB/s, 5,333.276 MB/s, 0.00485 TiB/s, 0.00533 TB/s) + |

| max memory channels | 1 + |

| microarchitecture | GS464 + |

| model number | 2E + |

| name | Godson-2E + |

| part number | CZ70 + |

| power dissipation | 7 W (7,000 mW, 0.00939 hp, 0.007 kW) + |

| process | 90 nm (0.09 μm, 9.0e-5 mm) + |

| series | Godson 2 + |

| smp max ways | 1 + |

| supported memory type | DDR-333 + |

| technology | CMOS + |

| thread count | 1 + |

| transistor count | 47,000,000 + |

| word size | 64 bit (8 octets, 16 nibbles) + |