From WikiChip

Difference between revisions of "ibm/microarchitectures/power8"

(→Octa-Core) |

|||

| (5 intermediate revisions by one other user not shown) | |||

| Line 35: | Line 35: | ||

| extension N = | | extension N = | ||

| − | | cache = | + | | cache = Yes |

| − | | l1i = | + | | l1i = 32 KiB |

| − | | l1i per = | + | | l1i per = core |

| − | | l1i desc = | + | | l1i desc = 8-way set associative |

| − | | l1d = | + | | l1d = 64 KiB |

| − | | l1d per = | + | | l1d per = core |

| − | | l1d desc = | + | | l1d desc = 8-way set associative |

| − | | l2 = | + | | l2 = 512 KiB |

| − | | l2 per = | + | | l2 per = core |

| l2 desc = | | l2 desc = | ||

| − | | l3 = | + | | l3 = 8 MiB |

| − | | l3 per = | + | | l3 per = core |

| l3 desc = | | l3 desc = | ||

| + | | l4 = 128 MiB | ||

| + | | l4 per = chip | ||

| + | | l4 desc = | ||

| core names = <!-- Yes if specify --> | | core names = <!-- Yes if specify --> | ||

| Line 57: | Line 60: | ||

| predecessor = POWER7+ | | predecessor = POWER7+ | ||

| predecessor link = ibm/microarchitectures/power7+ | | predecessor link = ibm/microarchitectures/power7+ | ||

| − | | successor = | + | | successor = POWER8+ |

| − | | successor link = ibm/microarchitectures/ | + | | successor link = ibm/microarchitectures/power8+ |

}} | }} | ||

'''POWER8''' is the [[Power]] microarchitecture for [[IBM]]'s family of {{ibm|POWER8}} processors that was introduced in [[2014]]. POWER8 is the successor to {{\\|POWER7+}}. | '''POWER8''' is the [[Power]] microarchitecture for [[IBM]]'s family of {{ibm|POWER8}} processors that was introduced in [[2014]]. POWER8 is the successor to {{\\|POWER7+}}. | ||

| + | |||

| + | == Architectures == | ||

| + | === Key changes from {{\\|POWER7}}/{{\\|POWER7+|+}} === | ||

| + | {{empty section}} | ||

| + | |||

| + | == Die == | ||

| + | === Dodeca-Core === | ||

| + | * [[Dodeca-Core]] | ||

| + | * IBM's [[22 nm process|22 nm SOI process]] | ||

| + | * 15 metal layers | ||

| + | * 4,200,000,000 transistors | ||

| + | * 649 mm² die size | ||

| + | : [[File:power8 die shot (12-core).png|750px]] | ||

| + | |||

| + | |||

| + | : [[File:power8 die shot (12-core)(annotated).png|750px]] | ||

| + | |||

| + | === Hexa-Core === | ||

| + | * [[hexa-core]] | ||

| + | * IBM's [[22 nm process|22 nm SOI process]] | ||

| + | * 15 metal layers | ||

| + | * 362 mm² die size | ||

| + | |||

| + | : ?die shot? | ||

| + | |||

| + | : [[File:power8 die shot (6-core)(annotated).png|450px]] | ||

Latest revision as of 14:30, 3 September 2017

| Edit Values | |

| POWER8 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | IBM |

| Manufacturer | IBM |

| Introduction | August, 2013 |

| Phase-out | June, 2014 |

| Process | 22 nm |

| Core Configs | 4, 6, 8, 10, 12 |

| Pipeline | |

| Type | Superscalar |

| Speculative | Yes |

| Reg Renaming | Yes |

| Stages | 15-23 |

| Cache | |

| L1I Cache | 32 KiB/core 8-way set associative |

| L1D Cache | 64 KiB/core 8-way set associative |

| L2 Cache | 512 KiB/core |

| L3 Cache | 8 MiB/core |

| L4 Cache | 128 MiB/chip |

| Succession | |

POWER8 is the Power microarchitecture for IBM's family of POWER8 processors that was introduced in 2014. POWER8 is the successor to POWER7+.

Architectures[edit]

Key changes from POWER7/+[edit]

| This section is empty; you can help add the missing info by editing this page. |

Die[edit]

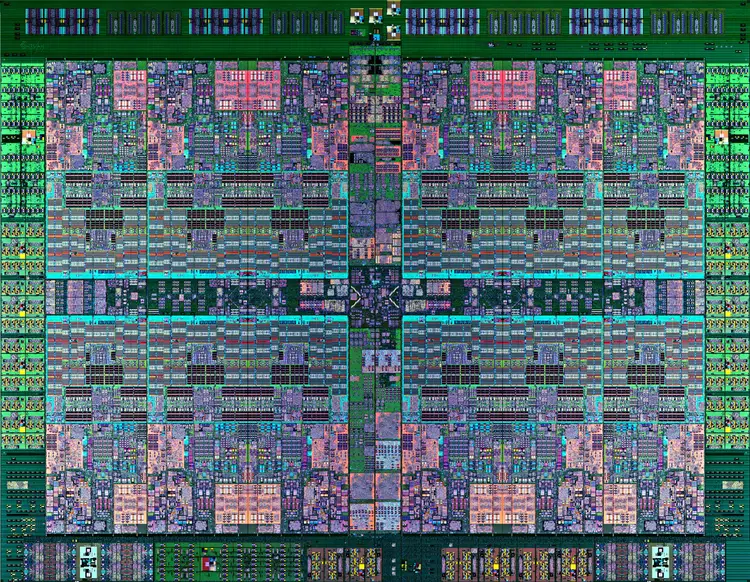

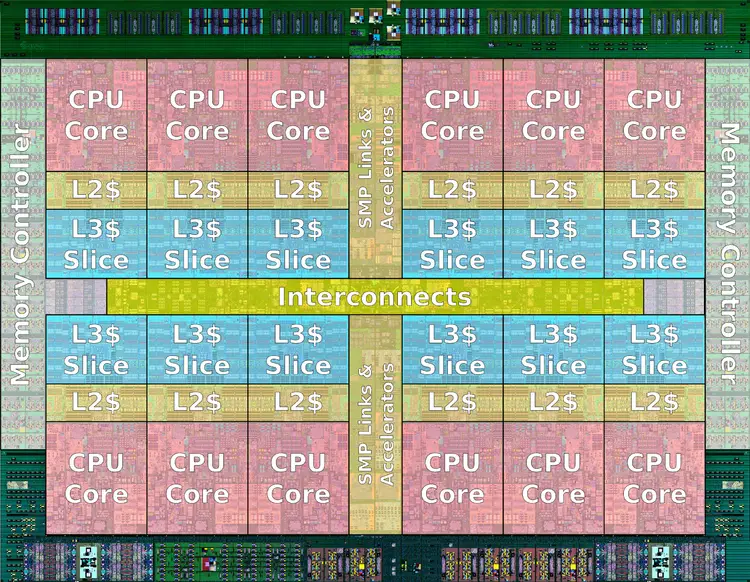

Dodeca-Core[edit]

- Dodeca-Core

- IBM's 22 nm SOI process

- 15 metal layers

- 4,200,000,000 transistors

- 649 mm² die size

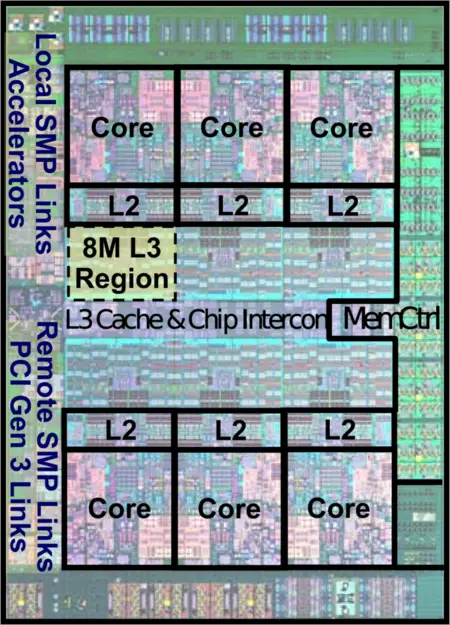

Hexa-Core[edit]

- hexa-core

- IBM's 22 nm SOI process

- 15 metal layers

- 362 mm² die size

- ?die shot?

Facts about "POWER8 - Microarchitectures - IBM"

| codename | POWER8 + |

| core count | 4 +, 6 +, 8 +, 10 + and 12 + |

| designer | IBM + |

| first launched | August 2013 + |

| full page name | ibm/microarchitectures/power8 + |

| instance of | microarchitecture + |

| manufacturer | IBM + |

| microarchitecture type | CPU + |

| name | POWER8 + |

| phase-out | June 2014 + |

| pipeline stages (max) | 23 + |

| pipeline stages (min) | 15 + |

| process | 22 nm (0.022 μm, 2.2e-5 mm) + |