(→P1) |

|||

| Line 88: | Line 88: | ||

<table class="comptable sortable tc4"> | <table class="comptable sortable tc4"> | ||

{{comp table header|main|7:List of QorIQ P1 Processors}} | {{comp table header|main|7:List of QorIQ P1 Processors}} | ||

| − | {{comp table header|cols| | + | {{comp table header|cols|Announced|Cores|Core|%Frequency|L2$|Max Power|Package}} |

{{#ask: [[Category:microprocessor models by freescale]] [[family::QorIQ]] [[series::P1]] | {{#ask: [[Category:microprocessor models by freescale]] [[family::QorIQ]] [[series::P1]] | ||

|?full page name | |?full page name | ||

|?model number | |?model number | ||

| − | |?first | + | |?first announced |

|?core count | |?core count | ||

|?core name | |?core name | ||

Revision as of 20:23, 31 October 2017

| QorIQ | |

| Developer | Freescale, NXP |

| Manufacturer | IBM, TSMC |

| Type | System on Chips |

| Introduction | June 16, 2008 (announced) June 16, 2008 (launch) |

| Architecture | POWER & ARM Communication SoC |

| Word size | 32 bit 4 octets , 64 bit8 nibbles 8 octets

16 nibbles |

| Process | 45 nm 0.045 μm , 32 nm4.5e-5 mm 0.032 μm , 20 nm3.2e-5 mm 0.02 μm , 16 nm2.0e-5 mm 0.016 μm

1.6e-5 mm |

| Technology | CMOS |

| Clock | 533 MHz-2,000 MHz |

| Succession | |

| ← | |

| PowerQUICC | |

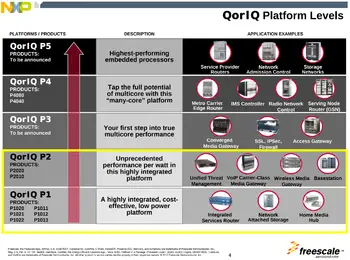

QorIQ (pronounced "Core IQ") is a family of ARM and POWER embedded and networking microprocessors designed and sold by NXP (formerly Freescale) since 2008 as a successor to the PowerQUICC family.

Overview

Introduced in 2008 by Freescale as a successor to the PowerQUICC family, then one of industry's most popular communications processors. Like the PowerQUICC brand, QorIQ spanned the entire range of products from low-power and low-cost to large multi-core designs. Original designs were based on the POWER architecture. In 2012 Freescale announced the Layerscape series that adopts the ARM architecture which Freescale/NXP has been using since.

Power

| This section requires expansion; you can help adding the missing info. |

Identification

Only applies to original QorIQ P & T series:

| Identification | ||||||||||||||

| QorIQ | P | 4 | 08 | 0 | ||||||||||

| QorIQ | P | 1 | 01 | 3 | ||||||||||

| Iteration/Version | ||||||||||||||

Core Count

| ||||||||||||||

| Platform Level | ||||||||||||||

Technology Node

| ||||||||||||||

Brand Name

| ||||||||||||||

P Series

Announced in mid-2008, the QorIQ P-series are POWER-based microprocessors based on the e500 microarchitecture. Being the first Freescale multicore networking applications based on the 45 nm process, those parts offered a migration path for PowerQUICC II Pro and PowerQUICC III processor customers. All chips are fully software compatible with each other and existing PowerQUICC processors with multi-core parts supporting both symmetric and asymmetric multiprocessing.

P1

The P1 series are designed for low-power fan-less design designed to succeed previous models (e.g., PowerQUICC II Pro) with higher performance at the same power envelope. All models exhibit a peak power consumption of sub 5 W. P1 parts are designed for the applications such as Ethernet switch controllers, gateways, wireless LAN access points, network printing/storage, and other networking devices with tight thermal constraints.

| List of QorIQ P1 Processors | |||||||

|---|---|---|---|---|---|---|---|

| Model | Announced | Cores | Core | Frequency | L2$ | Max Power | Package |

| P1010 | 16 June 2008 | 1 | e500 v2 | 667 MHz 0.667 GHz , 800 MHz667,000 kHz 0.8 GHz 800,000 kHz | 1.6 W 1,600 mW 0.00215 hp 0.0016 kW | TE-PBGA-II-689, TE-PBGA-425 | |

| P1011 | 16 June 2008 | 1 | e500 v2 | 800 MHz 0.8 GHz 800,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.56 W 1,560 mW 0.00209 hp 0.00156 kW | TE-PBGA-II-689 |

| P1012 | 7 December 2009 | 1 | e500 v2 | 533 MHz 0.533 GHz , 800 MHz533,000 kHz 0.8 GHz 800,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.6 W 1,600 mW 0.00215 hp 0.0016 kW | TE-PBGA-II-689 |

| P1013 | 9 September 2009 | 1 | e500 v2 | 1,067 MHz 1.067 GHz 1,067,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 3 W 3,000 mW 0.00402 hp 0.003 kW | TE-PBGA-II-689 |

| P1014 | 2010 | 1 | e500 v2 | 800 MHz 0.8 GHz 800,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.13 W 1,130 mW 0.00152 hp 0.00113 kW | TE-PBGA-II-689, TE-PBGA-425 |

| P1015 | October 2011 | 1 | e500 v2 | 400 MHz 0.4 GHz , 533 MHz400,000 kHz 0.533 GHz 533,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.4 W 1,400 mW 0.00188 hp 0.0014 kW | TE-PBGA-561 |

| P1016 | 1 | e500 v2 | 1.53 W 1,530 mW 0.00205 hp 0.00153 kW | TE-PBGA-561 | |||

| P1017 | 1 | e500 v2 | 2 W 2,000 mW 0.00268 hp 0.002 kW | TE-PBGA-457 | |||

| P1020 | 16 June 2008 | 2 | e500 v2 | 800 MHz 0.8 GHz 800,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.89 W 1,890 mW 0.00253 hp 0.00189 kW | TE-PBGA-II-689 |

| P1021 | 7 December 2009 | 2 | e500 v2 | 1,200 MHz 1.2 GHz 1,200,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 4.5 W 4,500 mW 0.00603 hp 0.0045 kW | TE-PBGA-II-689 |

| P1022 | 9 September 2009 | 2 | e500 v2 | 1,067 MHz 1.067 GHz 1,067,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 2.5 W 2,500 mW 0.00335 hp 0.0025 kW | TE-PBGA-II-689 |

| P1023 | 2 | e500 v2 | 2 W 2,000 mW 0.00268 hp 0.002 kW | TE-PBGA-457 | |||

| P1024 | October 2011 | 2 | e500 v2 | 533 MHz 0.533 GHz 533,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.6 W 1,600 mW 0.00215 hp 0.0016 kW | TE-PBGA-561 |

| P1025 | 2 | e500 v2 | 1.69 W 1,690 mW 0.00227 hp 0.00169 kW | TE-PBGA-561 | |||

| Count: 14 | |||||||

P2

The P2 series are designed to succeed the PowerQUICC III parts. These parts feature a large cache that may be configured as stashing memory, four Ethernet controllers with QoS features and flow control, DDR2/DDR3 SDRAM Controller with ECC support, four general purpose SerDes lanes that may be configured as either two Serial RapidIO ports, three PCI Express ports and two SGMII ports.

| List of QorIQ P2 Processors | ||||||

|---|---|---|---|---|---|---|

| Model | Launched | Cores | Core | Frequency | L2$ | Max Power |

| P2010 | 2009 | 1 | e500 v2 | 1,200 MHz 1.2 GHz 800 MHz1,200,000 kHz 0.8 GHz 1,000 MHz800,000 kHz 1 GHz 1,333 MHz1,000,000 kHz 1.333 GHz 1,333,000 kHz | 512 KiB 0.5 MiB 524,288 B 4.882812e-4 GiB | 6.7 W 6,700 mW 0.00898 hp 0.0067 kW |

| P2020 | 2009 | 2 | e500 v2 | 800 MHz 0.8 GHz 1,200 MHz800,000 kHz 1.2 GHz 1,333 MHz1,200,000 kHz 1.333 GHz 1,333,000 kHz | 512 KiB 0.5 MiB 524,288 B 4.882812e-4 GiB | 8 W 8,000 mW 0.0107 hp 0.008 kW |

| Count: 2 | ||||||

ARM

| This section is empty; you can help add the missing info by editing this page. |

See also

| designer | Freescale + and NXP + |

| first announced | June 16, 2008 + |

| first launched | June 16, 2008 + |

| full page name | nxp/qoriq + |

| instance of | system on a chip family + |

| main designer | Freescale + |

| manufacturer | IBM + and TSMC + |

| name | QorIQ + |

| process | 45 nm (0.045 μm, 4.5e-5 mm) +, 32 nm (0.032 μm, 3.2e-5 mm) +, 20 nm (0.02 μm, 2.0e-5 mm) + and 16 nm (0.016 μm, 1.6e-5 mm) + |

| technology | CMOS + |

| word size | 32 bit (4 octets, 8 nibbles) + and 64 bit (8 octets, 16 nibbles) + |