From WikiChip

Difference between revisions of "intel/microarchitectures/airmont"

(Created page with "{{intel title|Airmont|arch}} {{microarchitecture | name = Airmont | manufacturer = Intel | introduction = 2015 | phase-out = 2017 | process = 14 nm | core...") |

|||

| Line 69: | Line 69: | ||

| {{intel|Braswell}} || {{intel|Braswell}} || Tablets, PCs | | {{intel|Braswell}} || {{intel|Braswell}} || Tablets, PCs | ||

|} | |} | ||

| + | |||

| + | == Architecture== | ||

| + | Airmont is for the most part identical to {{intel|Silvermont}} with some higher number of execution units to the GPU in some of the higher-end models. | ||

| + | |||

| + | === Key changes from {{intel|Silvermont}} === | ||

| + | * DTLB table size doubled (128 entries -> 256 entries) | ||

| + | * L2 latency increased | ||

| + | * Reorder Buffer was increased (from 32 entries to 48) | ||

| + | * Gen 8 GPUs | ||

| + | === Block Diagram === | ||

| + | [[File:silvermont block.png]] | ||

| + | |||

| + | === Memory Hierarchy === | ||

| + | * Cache | ||

| + | ** Hardware prefetchers | ||

| + | ** L1 Cache: | ||

| + | *** 32 KB 8-way [[set associative]] instruction, 64 B line size | ||

| + | *** 24 KB 6-way set associative data, 64 B line size | ||

| + | *** Per core | ||

| + | ** L2 Cache: | ||

| + | *** 1 MB 16-way set associative, 64 B line size | ||

| + | *** Per 2 cores | ||

| + | ** L3 Cache: | ||

| + | *** No level 3 cache | ||

| + | ** RAM | ||

| + | *** Maximum of 1GB, 2 GB, and 4 GB | ||

| + | *** dual 32-bit channels, 1 or 2 ranks per channel | ||

| + | |||

| + | === Multithreading === | ||

| + | Silvermont dropped support for Intel Hyper-Threading Technology. | ||

| + | |||

| + | === Pipeline === | ||

| + | {{main|intel/microarchitectures/silvermont#Pipeline|l1=Silvermont's Pipeline}} | ||

| + | Airmont's pipeline is identical to {{intel|Silvermont|Silvermont's}}. | ||

| + | |||

| + | [[File:silvermont pipeline.svg]] | ||

| + | == Cores == | ||

| + | * {{intel|Cherry Trail}} - SoCs for Smartphones/Tablets | ||

| + | * {{intel|Braswell}} - SoCs for low-end PCs | ||

Revision as of 23:04, 9 April 2016

| Edit Values | |

| Airmont µarch | |

| General Info |

Airmont is Intel's 14 nm microarchitecture for the Atom family of system on chips. Introduced in 2015, Airmont is a shrink of Silvermont.

Contents

Codenames

| Platform | Core | Target |

|---|---|---|

| Cherry Trail | Cherry Trail | Smartphones, Tablets |

| Braswell | Braswell | Tablets, PCs |

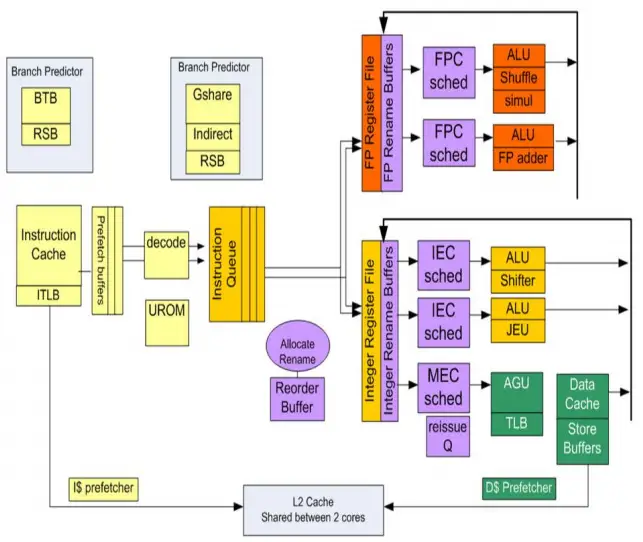

Architecture

Airmont is for the most part identical to Silvermont with some higher number of execution units to the GPU in some of the higher-end models.

Key changes from Silvermont

- DTLB table size doubled (128 entries -> 256 entries)

- L2 latency increased

- Reorder Buffer was increased (from 32 entries to 48)

- Gen 8 GPUs

Block Diagram

Memory Hierarchy

- Cache

- Hardware prefetchers

- L1 Cache:

- 32 KB 8-way set associative instruction, 64 B line size

- 24 KB 6-way set associative data, 64 B line size

- Per core

- L2 Cache:

- 1 MB 16-way set associative, 64 B line size

- Per 2 cores

- L3 Cache:

- No level 3 cache

- RAM

- Maximum of 1GB, 2 GB, and 4 GB

- dual 32-bit channels, 1 or 2 ranks per channel

Multithreading

Silvermont dropped support for Intel Hyper-Threading Technology.

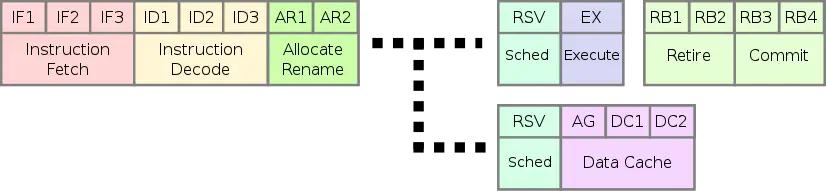

Pipeline

- Main article: Silvermont's Pipeline

Airmont's pipeline is identical to Silvermont's.

Cores

- Cherry Trail - SoCs for Smartphones/Tablets

- Braswell - SoCs for low-end PCs