From WikiChip

Difference between revisions of "phytium/feiteng/ft-2000+-64"

| (9 intermediate revisions by one other user not shown) | |||

| Line 10: | Line 10: | ||

|first announced=2019 | |first announced=2019 | ||

|first launched=2019 | |first launched=2019 | ||

| − | |family=FT-2000 | + | |family=FeiTeng |

| − | |frequency=2, | + | |series=FT-2000+ |

| + | |frequency=2,300 MHz | ||

|isa=ARMv8.0 | |isa=ARMv8.0 | ||

|isa family=ARM | |isa family=ARM | ||

|microarch=Mars II | |microarch=Mars II | ||

| + | |microarch 2=Xiaomi | ||

|core name=FTC-662 | |core name=FTC-662 | ||

|process=16 nm | |process=16 nm | ||

| Line 21: | Line 23: | ||

|die area=370 mm² | |die area=370 mm² | ||

|word size=64 bit | |word size=64 bit | ||

| + | |core count=64 | ||

| + | |thread count=64 | ||

| + | |max cpus=1 | ||

|tdp=96 W | |tdp=96 W | ||

|package name 1=phytium,fcbga_3576 | |package name 1=phytium,fcbga_3576 | ||

|predecessor=FT-2000/64 | |predecessor=FT-2000/64 | ||

| − | |predecessor link=phytium/ | + | |predecessor link=phytium/feiteng/ft-2000-64 |

}} | }} | ||

'''FT-2000+/64''' is a [[64 core]] [[ARM]] server SoC designed by [[Phytium]] and introduced in [[2019]]. Fabricated on [[TSMC]]'s [[16 nm process]], the chip operates at up 2.3 GHz with a TDP of 96 W. This chip is designed for server, communication, and infrastructure applications. | '''FT-2000+/64''' is a [[64 core]] [[ARM]] server SoC designed by [[Phytium]] and introduced in [[2019]]. Fabricated on [[TSMC]]'s [[16 nm process]], the chip operates at up 2.3 GHz with a TDP of 96 W. This chip is designed for server, communication, and infrastructure applications. | ||

| + | |||

| + | == Cache == | ||

| + | {{main|phytium/microarchitectures/mars_ii#Memory_Hierarchy|l1=Mars II § Cache}} | ||

| + | {{cache size | ||

| + | |l1 cache=4 MiB | ||

| + | |l1i cache=2 MiB | ||

| + | |l1i break=64x32 KiB | ||

| + | |l1d cache=2 MiB | ||

| + | |l1d break=64x32 KiB | ||

| + | |l2 cache=32 MiB | ||

| + | |l2 break=16x2 MiB | ||

| + | }} | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=DDR4-3200 | ||

| + | |ecc=Yes | ||

| + | |controllers=8 | ||

| + | |channels=8 | ||

| + | |max bandwidth=143.1 GiB/s | ||

| + | |bandwidth schan=17.88 GiB/s | ||

| + | |bandwidth dchan=35.76 GiB/s | ||

| + | |bandwidth qchan=71.53 GiB/s | ||

| + | |bandwidth hchan=107.3 GiB/s | ||

| + | |bandwidth ochan=143.1 GiB/s | ||

| + | }} | ||

| + | |||

| + | == Expansions == | ||

| + | {{expansions | ||

| + | | pcie revision = 3.0 | ||

| + | | pcie lanes = 33 | ||

| + | | pcie config = 4x8+x1 | ||

| + | | pcie config 2 = | ||

| + | | sata revision = | ||

| + | | sata ports = | ||

| + | | usb revision = | ||

| + | | usb revision 2 = | ||

| + | | usb ports = | ||

| + | | usb rate = | ||

| + | | uart = | ||

| + | | uart ports = | ||

| + | | gp io = | ||

| + | }} | ||

| + | |||

| + | == Die == | ||

| + | {{main|phytium/microarchitectures/mars_ii#Die|l1=Mars II § Die}} | ||

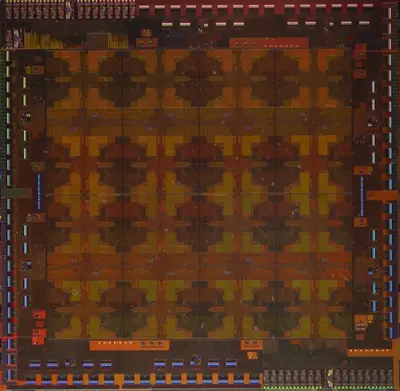

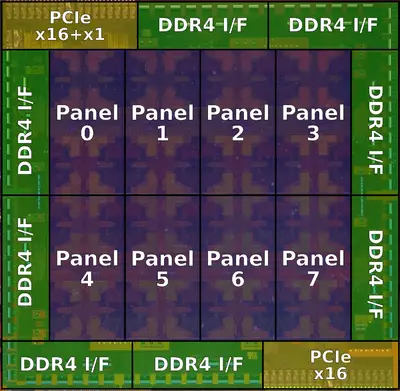

| + | :[[File:mars ii die.png|400px]] | ||

| + | |||

| + | |||

| + | :[[File:mars ii die (annotated).png|400px]] | ||

Latest revision as of 03:41, 17 July 2023

| Edit Values | |

| FT-2000+/64 | |

| |

| General Info | |

| Designer | Phytium |

| Manufacturer | TSMC |

| Model Number | FT-2000+/64 |

| Market | Server |

| Introduction | 2019 (announced) 2019 (launched) |

| General Specs | |

| Family | FeiTeng |

| Series | FT-2000+ |

| Frequency | 2,300 MHz |

| Microarchitecture | |

| ISA | ARMv8.0 (ARM) |

| Microarchitecture | Mars II, Xiaomi |

| Core Name | FTC-662 |

| Process | 16 nm |

| Transistors | 6,000,000,000 |

| Technology | CMOS |

| Die | 370 mm² |

| Word Size | 64 bit |

| Cores | 64 |

| Threads | 64 |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| TDP | 96 W |

| Packaging | |

| Package | FCBGA-3576 (BGA) |

| Dimension | 61 mm × 61 mm |

| Contacts | 3576 |

| |

| Succession | |

FT-2000+/64 is a 64 core ARM server SoC designed by Phytium and introduced in 2019. Fabricated on TSMC's 16 nm process, the chip operates at up 2.3 GHz with a TDP of 96 W. This chip is designed for server, communication, and infrastructure applications.

Contents

Cache[edit]

- Main article: Mars II § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||

|

||||||||||||

Expansions[edit]

|

Expansion Options

|

||||||||

|

||||||||

Die[edit]

- Main article: Mars II § Die

Facts about "FT-2000+/64 - Phytium"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | FT-2000+/64 - Phytium#io + |

| back image |  + + |

| base frequency | 2,300 MHz (2.3 GHz, 2,300,000 kHz) + |

| core count | 64 + |

| core name | FTC-662 + |

| designer | Phytium + |

| die area | 370 mm² (0.574 in², 3.7 cm², 370,000,000 µm²) + |

| family | FeiTeng + |

| first announced | 2019 + |

| first launched | 2019 + |

| full page name | phytium/feiteng/ft-2000+-64 + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| isa | ARMv8.0 + |

| isa family | ARM + |

| l1$ size | 4,096 KiB (4,194,304 B, 4 MiB) + |

| l1d$ size | 2,048 KiB (2,097,152 B, 2 MiB) + |

| l1i$ size | 2,048 KiB (2,097,152 B, 2 MiB) + |

| l2$ size | 32 MiB (32,768 KiB, 33,554,432 B, 0.0313 GiB) + |

| ldate | 2019 + |

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Server + |

| max cpu count | 1 + |

| max memory bandwidth | 143.1 GiB/s (146,534.4 MiB/s, 153.652 GB/s, 153,652.455 MB/s, 0.14 TiB/s, 0.154 TB/s) + |

| max memory channels | 8 + |

| max pcie lanes | 33 + |

| microarchitecture | Mars II + and Xiaomi + |

| model number | FT-2000+/64 + |

| name | FT-2000+/64 + |

| package | FCBGA-3576 + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |

| series | FT-2000+ + |

| smp max ways | 1 + |

| supported memory type | DDR4-3200 + |

| tdp | 96 W (96,000 mW, 0.129 hp, 0.096 kW) + |

| technology | CMOS + |

| thread count | 64 + |

| transistor count | 6,000,000,000 + |

| word size | 64 bit (8 octets, 16 nibbles) + |