From WikiChip

Godson-2F - Loongson

| Edit Values | |

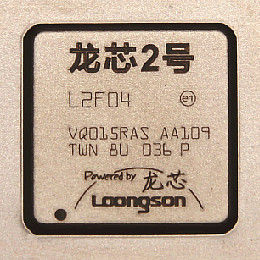

| Godson-2F | |

| |

| Godson-2F chip | |

| General Info | |

| Designer | Loongson |

| Manufacturer | STMicroelectronics |

| Model Number | 2F |

| Part Number | PLA80 |

| Market | Desktop |

| Introduction | July 31, 2007 (announced) June, 2008 (launched) |

| General Specs | |

| Family | Godson 2 |

| Series | Godson 2 |

| Frequency | 800 MHz |

| Microarchitecture | |

| ISA | MIPS64 (MIPS) |

| Microarchitecture | GS464 |

| Core Name | GS464 |

| Process | 90 nm |

| Transistors | 51,000,000 |

| Technology | CMOS |

| Die | 43 mm² |

| Word Size | 64 bit |

| Cores | 1 |

| Threads | 1 |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| Power dissipation | 5 W |

| Vcore | 1.2 V |

Godson-2F (龙芯2F) is a 64-bit MIPS performance processor developed by ICT and later Loongson for desktop computers. Introduced in mid-2008, the Godson-2F operates at up to 800 MHz consuming 5 W. This chip was manufactured on STMicroelectronics' 90 nm process.

The Godson-2F features a faster memory controller (supporting up to DDR2-667) and integrates some of the functionality of the southbridge including a PCI-X controller and more general-purpose I/O pins.

Cache[edit]

- Main article: GS464 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions[edit]

This chip has integrated HyperTransport 1.0 operating at 400 MHz.

|

Expansion Options

|

||||||||||||||||||||

|

||||||||||||||||||||

Graphics[edit]

This chip had no integrated graphics processing unit.

Die Shot[edit]

- 90 nm process

- 51,000,000 transistors

- 43 mm² die size

Datasheet[edit]

References[edit]

- Hu, Wei-Wu, and Jian Wang. "Making effective decisions in computer architects’ real-world: Lessons and experiences with Godson-2 processor designs." Journal of Computer Science and Technology 23.4 (2008): 620-632.

Facts about "Godson-2F - Loongson"

| base frequency | 800 MHz (0.8 GHz, 800,000 kHz) + |

| core count | 1 + |

| core name | GS464 + |

| core voltage | 1.2 V (12 dV, 120 cV, 1,200 mV) + |

| designer | Loongson + |

| die area | 43 mm² (0.0667 in², 0.43 cm², 43,000,000 µm²) + |

| family | Godson 2 + |

| first announced | July 31, 2007 + |

| first launched | June 2008 + |

| full page name | loongson/godson 2/2f + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| isa | MIPS64 + |

| isa family | MIPS + |

| l1$ size | 128 KiB (131,072 B, 0.125 MiB) + |

| l1d$ description | 4-way set associative + |

| l1d$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l2$ description | 4-way set associative + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| ldate | June 2008 + |

| main image |  + + |

| main image caption | Godson-2F chip + |

| manufacturer | STMicroelectronics + |

| market segment | Desktop + |

| max cpu count | 1 + |

| max memory bandwidth | 9.934 GiB/s (10,172.416 MiB/s, 10.667 GB/s, 10,666.551 MB/s, 0.0097 TiB/s, 0.0107 TB/s) + |

| max memory channels | 1 + |

| microarchitecture | GS464 + |

| model number | 2F + |

| name | Godson-2F + |

| part number | PLA80 + |

| power dissipation | 5 W (5,000 mW, 0.00671 hp, 0.005 kW) + |

| process | 90 nm (0.09 μm, 9.0e-5 mm) + |

| series | Godson 2 + |

| smp max ways | 1 + |

| supported memory type | DDR2-667 + |

| technology | CMOS + |

| thread count | 1 + |

| transistor count | 51,000,000 + |

| word size | 64 bit (8 octets, 16 nibbles) + |