From WikiChip

MT6595 - MediaTek

| Edit Values | |

| MT6595 | |

| General Info | |

| Designer | MediaTek, ARM Holdings |

| Manufacturer | TSMC |

| Model Number | MT6595 |

| Part Number | MT6595 |

| Market | Mobile |

| Introduction | Februray 11, 2014 (announced) Februray 11, 2014 (launched) |

| General Specs | |

| Family | MT65xx |

| Frequency | 2,500 MHz, 1,700 MHz |

| Microarchitecture | |

| ISA | ARMv7 (ARM) |

| Microarchitecture | Cortex-A17, Cortex-A7 |

| Core Name | Cortex-A17, Cortex-A7 |

| Process | 28 nm |

| Technology | CMOS |

| Die | 89 mm² |

| Word Size | 64 bit |

| Cores | 8 |

| Threads | 8 |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

MT6595 is a mid-range octa-core ARM LTE SoC designed by MediaTek and introduced in early 2014. This chip, which is fabricated on TSMC's 28 nm process, features four big Cortex-A17 cores operating at up to 2.5 GHz and four little Cortex-A7 cores operating at up to 1.7 GHz. The MT6595 incorporates an PowerVR G6200 GPU operating at up to 600 MHz and supports up to dual-channel LPDDR3-1866 memory.

Contents

Cache[edit]

- Main article: Cortex-A7 § Cache

Cortex-A7 Cluster:

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

||||||||

|

||||||||

Cortex-A17 Cluster:

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

||||||||

|

||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||

|

||||||||

Graphics[edit]

|

Integrated Graphics Information

|

||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||

- Encoding H.265

- Playback H.264, H.265 / HEVC, VP-9

Camera[edit]

- Image signal processor

- 20 Mpixel

Connectivity[edit]

- UE Cat-4

- EDGE, FDD / TDD LTE, HSPA +, TD-SCDMA

- Bluetooth

- Wi-Fi

- a/b/g/n/ac

Location[edit]

- GNSS

- GPS, Glonass, Beidou, Galileo

Utilizing devices[edit]

- Gionee P7 Max

- InFocus M530

- Zopo ZP999

- Meizu MX4

This list is incomplete; you can help by expanding it.

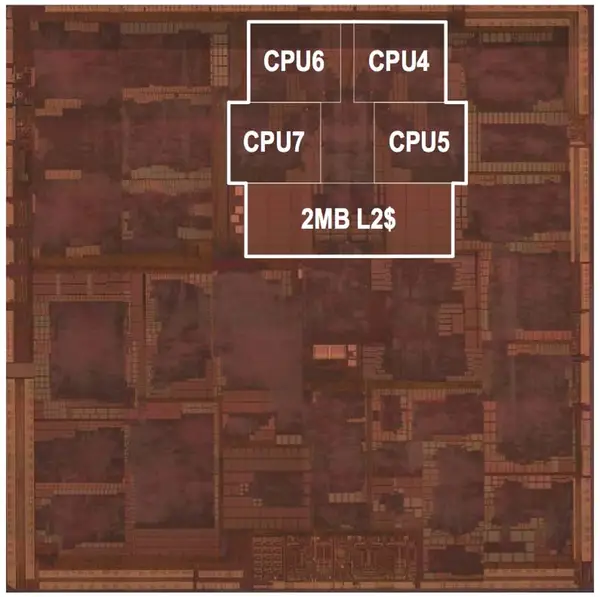

Die[edit]

- TSMC 28 nm process

- 89 mm² die size

- Quad-core Cortex-A7

- ~0.48 mm² per core

- Quad-core Cortex-A17 + 2 MiB L2

- ~1.93 mm² per core

- ~3.93 mm² for 2 MiB L2

(small quad-core is unlabeled below the big core cluster)

Bibliography[edit]

- Mair, Hugh, et al. "23.3 A highly integrated smartphone SoC featuring a 2.5 GHz octa-core CPU with advanced high-performance and low-power techniques." Solid-State Circuits Conference-(ISSCC), 2015 IEEE International. IEEE, 2015.

Categories:

- all microprocessor models

- microprocessor models by mediatek

- microprocessor models by mediatek based on cortex-a17

- microprocessor models by mediatek based on cortex-a7

- microprocessor models by arm holdings

- microprocessor models by arm holdings based on cortex-a17

- microprocessor models by arm holdings based on cortex-a7

- microprocessor models by tsmc

Facts about "MT6595 - MediaTek"

| base frequency | 2,500 MHz (2.5 GHz, 2,500,000 kHz) + and 1,700 MHz (1.7 GHz, 1,700,000 kHz) + |

| core count | 8 + |

| core name | Cortex-A17 + and Cortex-A7 + |

| designer | MediaTek + and ARM Holdings + |

| die area | 89 mm² (0.138 in², 0.89 cm², 89,000,000 µm²) + |

| family | MT65xx + |

| first announced | November 2014 + |

| first launched | November 2014 + |

| full page name | mediatek/mt65xx/mt6595 + |

| has ecc memory support | false + |

| instance of | microprocessor + |

| integrated gpu | PowerVR G6200 + |

| integrated gpu base frequency | 600 MHz (0.6 GHz, 600,000 KHz) + |

| integrated gpu designer | Imagination Technologies + |

| isa | ARMv7 + |

| isa family | ARM + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + and 2 MiB (2,048 KiB, 2,097,152 B, 0.00195 GiB) + |

| ldate | November 2014 + |

| manufacturer | TSMC + |

| market segment | Mobile + |

| max cpu count | 1 + |

| max memory channels | 2 + |

| microarchitecture | Cortex-A17 + and Cortex-A7 + |

| model number | MT6595 + |

| name | MT6595 + |

| part number | MT6595 + |

| process | 28 nm (0.028 μm, 2.8e-5 mm) + |

| smp max ways | 1 + |

| supported memory type | LPDDR3-1866 + |

| technology | CMOS + |

| thread count | 8 + |

| used by | Gionee P7 Max +, InFocus M530 +, Zopo ZP999 + and Meizu MX4 + |

| word size | 64 bit (8 octets, 16 nibbles) + |