From WikiChip

Cortex-A17 - Microarchitectures - ARM

| Edit Values | |

| Cortex-A17 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | ARM Holdings |

| Manufacturer | TSMC |

| Introduction | February 11, 2014 |

| Instructions | |

| ISA | ARMv7 |

| Succession | |

Cortex-A17 is the successor to the Cortex-A12, a mid-range performance ARM microarchitecture designed by ARM Holdings for the mobile market. This microarchitecture is designed as a synthesizable IP core and is sold to other semiconductor companies to be implemented in their own chips. The Cortex-A17 was designed to be paired with the low-power Cortex-A7 in a big.LITTLE configuration.

Contents

Architecture[edit]

Key changes from Cortex-A12[edit]

| This section is empty; you can help add the missing info by editing this page. |

Block Diagram[edit]

| This section is empty; you can help add the missing info by editing this page. |

Memory Hierarchy[edit]

| This section is empty; you can help add the missing info by editing this page. |

Licensees[edit]

Arm named the following companies as licensees.

Die[edit]

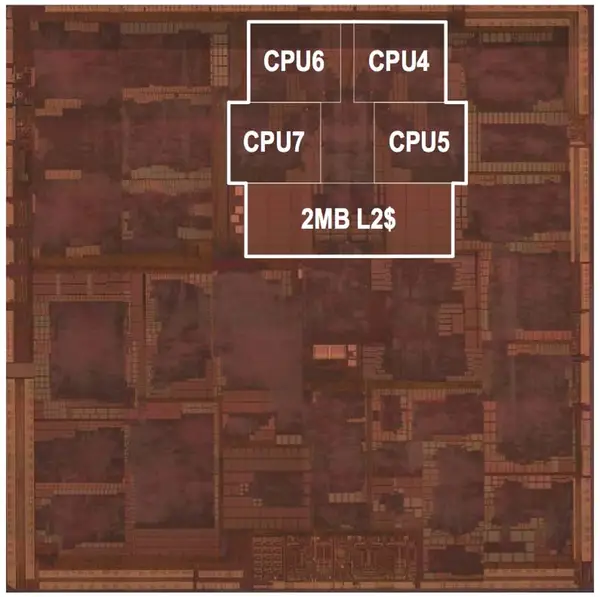

MediaTek MT6595[edit]

- TSMC 28 nm process

- 89 mm² die size

- Quad-core Cortex-A7

- ~0.48 mm² per core

- Quad-core Cortex-A17 + 2 MiB L2

- ~1.93 mm² per core

- ~3.93 mm² for 2 MiB L2

(small quad-core is unlabeled below the big core cluster)

Bibliography[edit]

- Mair, Hugh, et al. "23.3 A highly integrated smartphone SoC featuring a 2.5 GHz octa-core CPU with advanced high-performance and low-power techniques." Solid-State Circuits Conference-(ISSCC), 2015 IEEE International. IEEE, 2015.

Facts about "Cortex-A17 - Microarchitectures - ARM"

| codename | Cortex-A17 + |

| designer | ARM Holdings + |

| first launched | February 11, 2014 + |

| full page name | arm holdings/microarchitectures/cortex-a17 + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv7 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Cortex-A17 + |