| Ambric Am2000 | |

| |

| Am2045 | |

| Developer | Ambric |

| Manufacturer | TSMC |

| Type | Microprocessors |

| Introduction | October 10, 2006 (announced) December, 2006 (launch) |

| Production | 2007-2013 |

| Architecture | Many-core 32-bit microprocessor |

| Word size | 32 bit 4 octets

8 nibbles |

| Process | 130 nm 0.13 μm

1.3e-4 mm |

| Technology | CMOS |

| Clock | 1 MHz-350 Mhz |

| Package | FCBGA-868, FCBGA-896 |

Am2000 was a family of 32-bit MPPAs designed by Ambric. The series was introduced at the 2006 Fall Microprocessor Forum. The two flagship models the Am2045 (A) and later Am2045B had over 300 cores with maximum theoretical performance of over one trillion operations per second. Due to the economic downturn of 2008 Ambric failed to secure additional funding and was forced to sell its assets to Nethra Imaging which continued to manufacture the chips until 2013. Prior to the acquisition Ambric also announced a 600 cores, 600 MHz model. It's unknown if the model ever made it to market. Designs, software, and related patents are now held by Imagination Technologies.

Ambric, unlike many of its competitors, managed to develop a sound programming model that proved itself to be simple enough and intuitive enough to allow easy programming. Am2000 found their way to various military applications, medical instruments, and high-end multimedia hardware.

Contents

Overview[edit]

Introduced in the fall of 2006, the Am2000 is a series of many-core processors implemented as a massively parallel processor array designed to replace high-end embedded processors, DSPs, and FPGAs in applications where fast general-purpose integer arithmetic and digital-signal processing is required. Such tasks usually land themselves fairly well in highly parallel environments.

Ambric's AM2000 series is an example of one of the few massively parallel processors that succeeded in independently developing a solid programming model and tools that worked extremely well with the underlying processor that relatively easy to code. A complete set of development tools were also offered with the product including extensions to Eclipse IDE. Code for the AM2000 used a language called aJava which was a strict subset of Java that compiled directly into machine code.

Members[edit]

,,,,,,,| Am2000 Models | ||||

|---|---|---|---|---|

| Model | Launched | Process | Freq | Core Count |

| Am2012 | January 2007 | 130 nm 0.13 μm 1.3e-4 mm | 333 MHz 0.333 GHz 333,000 kHz | 96 |

| Am2016 | 15 November 2007 | 130 nm 0.13 μm 1.3e-4 mm | 350 MHz 0.35 GHz 350,000 kHz | 120 |

| Am2024 | January 2007 | 130 nm 0.13 μm 1.3e-4 mm | 333 MHz 0.333 GHz 333,000 kHz | 192 |

| Am2029 | 15 November 2007 | 130 nm 0.13 μm 1.3e-4 mm | 350 MHz 0.35 GHz 350,000 kHz | 216 |

| Am2035 | January 2007 | 130 nm 0.13 μm 1.3e-4 mm | 333 MHz 0.333 GHz 333,000 kHz | 280 |

| Am2045 | January 2007 | 130 nm 0.13 μm 1.3e-4 mm | 333 MHz 0.333 GHz 333,000 kHz | 344 |

| Am2045B | 15 November 2007 | 130 nm 0.13 μm 1.3e-4 mm | 350 MHz 0.35 GHz 350,000 kHz | 344 |

| Am2070 | 90 nm 0.09 μm 9.0e-5 mm | 600 MHz 0.6 GHz 600,000 kHz | 560 | |

| Count: 8 | ||||

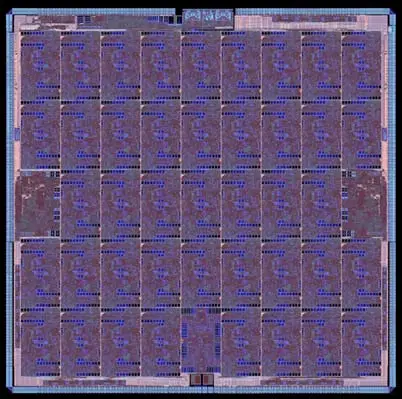

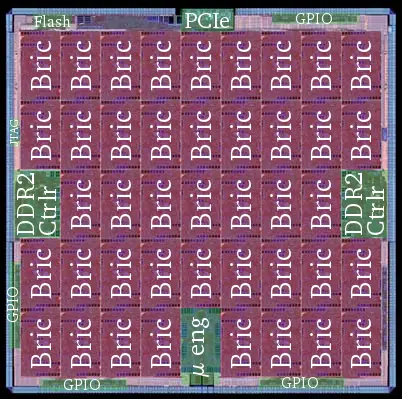

Die Shot[edit]

Am2045[edit]

|

|

Architecture[edit]

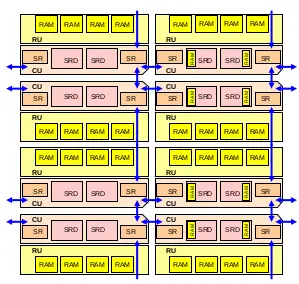

Ambric's Am2000 models are all made of small homogeneous units called Brics. The exact number of brics depends on the model.

Communication[edit]

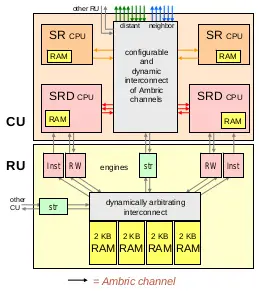

Ambric's architecture makes heavy use of Ambric Channels - self-synchronized and asynchronous interconnects that carry both data and instructions across the chip. Channels are a strong point of this architecture as all data goes through channels including memory and the pipeline itself. Channel interconnects can be loosely divided into three categories:

- Intra-Bric Channels: internal channels that span no loner than a single bric. All basic communication utilizes these channels. They are dynamically configured by the instructions themselves. The datapath itself is also an Ambric channel.

- Neighbor Channels: channels spanning between two CU units. These channels only go to an adjacent control unit (i.e. directly North, South, East, or West). Only one channel is aviable in each direction. Channels are 32-bit wide operating at up to 9.6 GT/s.

- Inter-Bric Channels: also known as distanced bric channels, are communication channels that operate globally between any two brics. Switches are located at each of the control units (CUs). Routes are configured statically.

An Ambric Channels can be more concisely define as a chain of Ambric registers. Ambric registers are simple 32-bit storage units with both data in port and data out port as well two control signals - valid and accept. The two control signals allow registers to be self-synchronized and operate asynchronously. The accept signal is asserted when input can be written. The valid signal is asserted, when it has output available. Assertion of both signals would indicate transfer. This setup allows input and output to also operate at different clock rates to accommodate different workloads.

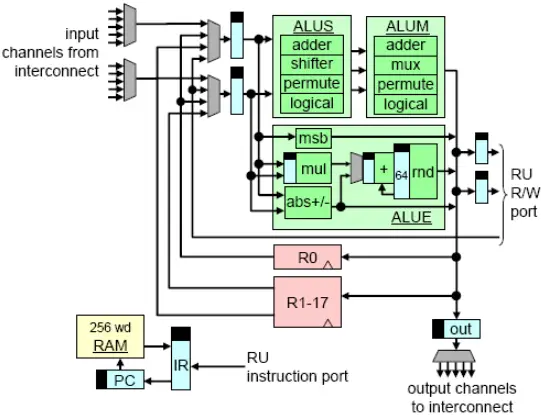

Brics[edit]

Bric is the fundamental building block. Each block contains:

- 2x Compute Units (CU)

- 2x RAM Units (RU)

- Each RAM Unit contains 4 2 kB RAM banks, each independently accessed via a dynamically programmed channel operating in FIFO and random access modes via the RU engines. RUs are used for temporary data and buffering largely used for local operations. On-die storage is kept simple, fast, and efficient.

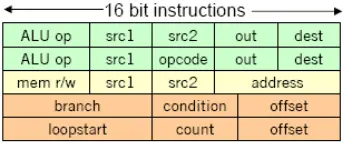

SR Processor[edit]

The SR (Streaming RISC) Processor is a 32-bit processor for fast simple operations. The datapath itself is a self-synchronizing Ambric Channel with 3-stages. This processor can handle complex addressing, serialization and deserialization. Each processor has 2 input channels and 1 output channel - all of which are controlled by the instructions themselves. Additionally, the processor includes:

- 1x ALU - 1x 32-bit OR 2x 16-bit operations

- 8x General Purpose Registers

- 16-bit instruction word size

- 64 word local code/data RAM

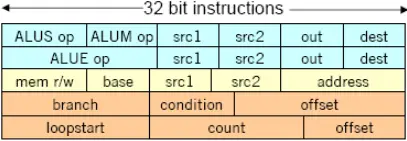

SRD Processor[edit]

The SRD (Streaming RISC with DSP extensions) Processor is a 32-bit processor for more complex operations that may benefit from instruction-level parallelism and iterative algorithms. The datapath itself is a self-synchronizing Ambric Channel with 3-stages. Each processor has 2 input channels and 1 output channel - all of which are controlled by the instructions themselves. Additionally, the processor includes:

- 3x ALU

Programming[edit]

Programming may be done in assembly or in aJava. aJava is a strict subset of Java. While it excludes the Java standard library, Ambric did offer various libraries for performing various video and imaging processing (e.g. AVC-Intra, MPEG-2. H.264, JPEG 2000, DVCPRO HD).

Ambric employed a Structural Object Programming Model. Every object is strictly encapsulated. Because the large number of cores each chip offers, objects are treated as independent programs running concurrently. Objects exchange data and control only through structures called Ambric channels which are both self-synchronizing and operate asynchronously.

Tools[edit]

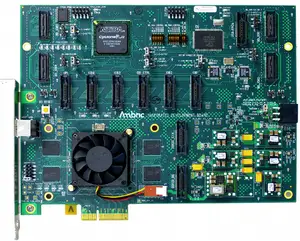

- Am2045 Software Development Board

- 1x production Am2045 + SDRAM

- PCI Express interface to host

- For rapid software development

- Am2045 Integrated Development Board

Applications[edit]

The Am2000 has been used for high-definition video processing, medical imaging devices, high performance network processing, image recognition, and various military applications such as drones.

Documents[edit]

- The Ambric Processor Array, 2006

- TeraOPS Hardware A New Massively-Parallel MIMD Computing Fabric IC, 2006

- A Structural Object Programming Model, Architecture, Chip and Tools for Reconfigurable Computing, 2007

- Ambric University Intro, 2008

Papers[edit]

- Butts, Michael, Anthony Mark Jones, and Paul Wasson. "A structural object programming model, architecture, chip and tools for reconfigurable computing." Proceedings of IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM). 2007.

- Qasim, Muhammad, and Chaudhry Majid Ali. "Signal Processing on Ambric Processor Array: Baseband processing in radio base stations." (2008). Halmstad University.

- Biedermann, Alexander. "Theoretische und algorithmische Evaluation eines massiv-parallelen Multiprozessorarrays der Ambric Am2000-Familie unter Verwendung von Videoalgorithmen. Diss. 2008.

See also[edit]

| designer | Ambric + |

| first announced | October 10, 2006 + |

| first launched | December 2006 + |

| full page name | ambric/am2000 + |

| instance of | microprocessor family + |

| main designer | Ambric + |

| manufacturer | TSMC + |

| name | Ambric Am2000 + |

| package | FCBGA-868 + and FCBGA-896 + |

| process | 130 nm (0.13 μm, 1.3e-4 mm) + |

| technology | CMOS + |

| word size | 32 bit (4 octets, 8 nibbles) + |