From WikiChip

Difference between revisions of "intel/microarchitectures/netburst (client)"

| Line 22: | Line 22: | ||

== Die == | == Die == | ||

| + | === Willamette === | ||

* {{intel|Willamette|l=core}} core | * {{intel|Willamette|l=core}} core | ||

* [[180 nm process]] | * [[180 nm process]] | ||

| Line 29: | Line 30: | ||

:[[File:netburst willamette core die.png|700px]] | :[[File:netburst willamette core die.png|700px]] | ||

| + | |||

| + | === Northwood === | ||

| + | * {{intel|Northwood|l=core}} core | ||

| + | * [[130 nm process]] | ||

| + | * 131 mm² die size | ||

| + | * 55,000,000 transistors | ||

| + | |||

| + | |||

| + | :[[File:netburst northwood core die.png|700px]] | ||

| + | |||

| + | |||

| + | === Prescott === | ||

| + | * {{intel|Prescott|l=core}} core | ||

| + | * [[90 nm process]] | ||

| + | * 135 mm² die size | ||

| + | * 169,000,000 transistors | ||

| + | |||

| + | |||

| + | :[[File:netburst prescott core die.png|700px]] | ||

=== Additional Shots === | === Additional Shots === | ||

Revision as of 00:36, 10 April 2018

| Edit Values | |

| NetBurst µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | November 20, 2000 |

| Phase-out | April, 2006 |

| Process | 180 nm |

| Instructions | |

| ISA | x86-32, x86-64 |

| Succession | |

NetBurst (also P68) was the microarchitecture for Intel's 180 nm process for desktops and servers as a successor to P6. NetBurst was replaced by the Core microarchitecture in early 2006.

Die

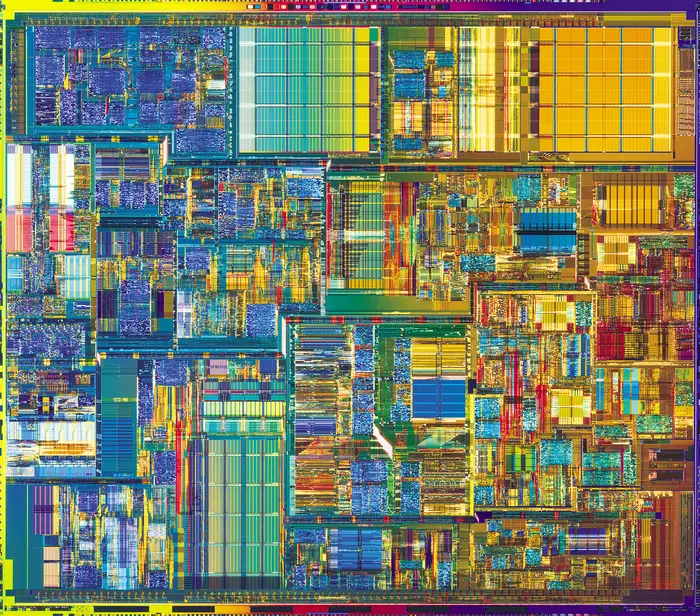

Willamette

- Willamette core

- 180 nm process

- 217 mm² die size

- 42,000,000 transistors

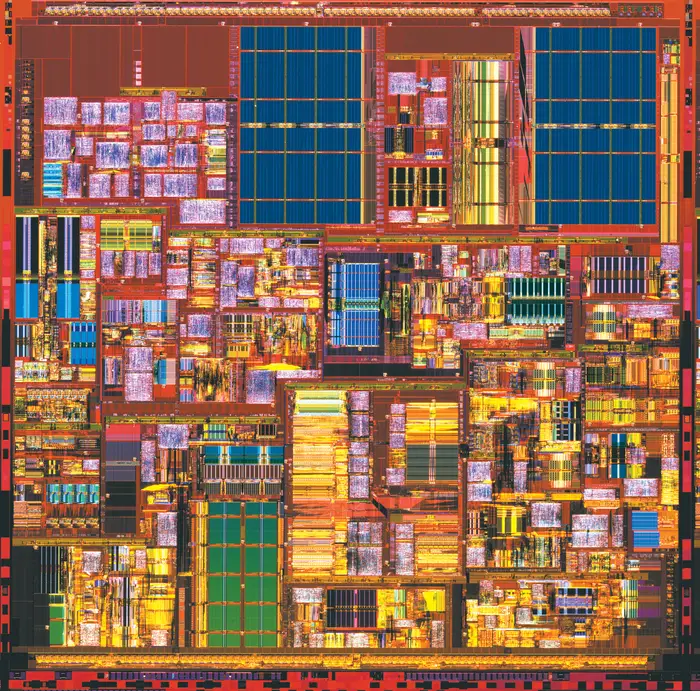

Northwood

- Northwood core

- 130 nm process

- 131 mm² die size

- 55,000,000 transistors

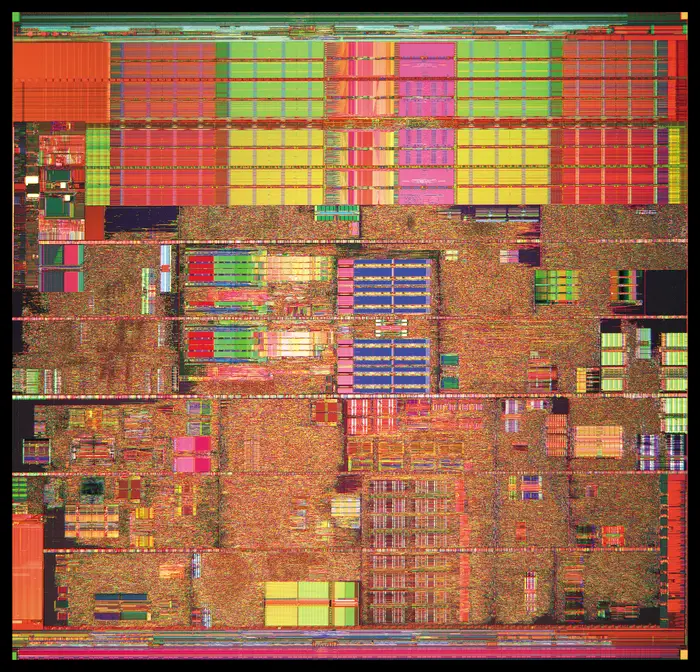

Prescott

- Prescott core

- 90 nm process

- 135 mm² die size

- 169,000,000 transistors

Additional Shots

Additional die and wafer shots provided by Intel:

Facts about "NetBurst - Microarchitectures - Intel"

| codename | NetBurst + |

| designer | Intel + |

| first launched | November 20, 2000 + |

| full page name | intel/microarchitectures/netburst (client) + |

| instance of | microarchitecture + |

| instruction set architecture | x86-32 + and x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | NetBurst + |

| phase-out | April 2006 + |

| process | 180 nm (0.18 μm, 1.8e-4 mm) + |