From WikiChip

Package FP3 - AMD

| Edit Values | |

| Package FP3 | |

| General Info | |

| Designer | AMD |

| Introduction | June 2014 (launched) |

| Market | Mobile, Embedded |

| Microarchitecture | Steamroller |

| TDP | 35 W 35,000 mW 0.0469 hp 0.035 kW |

| Package | |

| Name | BGA-854 |

| Type | Organic Micro Ball Grid Array |

| Contacts | 854 |

| Dimension | 29 mm 2.9 cm × 32 mm1.142 in 3.2 cm 1.26 in |

| Pitch | 0.8-1.2 mm "-1.2mm" is not declared as a valid unit of measurement for this property. |

FP3 is a BGA-854 package for AMD mobile and embedded microprocessors with integrated graphics. Its counterpart for desktop processors is the PGA-906 package for Socket FM2+. FP3 is the successor to the FP2 package and was superseded by the FP4 package.

All processors in the FP3 package are members of AMD's Family 15h with CPU cores based on the Steamroller microarchitecture, and are fabricated on a 28 nm SOI process.

Contents

Features

- 854-pin lidless micro ball grid array package, 0.8-1.2 mm multi-pitch, 29 × 32 mm, organic substrate

- 2 × 64/72 bit DDR3 SDRAM interface up to 1067 MHz, PC3-17000 (DDR3-2133), 34.1 GB/s

- Up to 2 SR/DR UDIMMs or SODIMMs (1 per channel), ECC supported

- JEDEC 1.5V, 1.35V, 1.25V

- AMD Memory Controller PowerCap

- PCIe Gen 1.0, 2.0, 3.0 (8 GT/s)

- Configurable x16 external graphics card (GFX) link (x16, x8, x4, up to 2 ports, DDI)

- PCIe Gen 1.0, 2.0 (5 GT/s)

- Configurable x8 General Purpose Ports (x4, x2, x1, up to 5 ports, DDI)

- x4 Unified Media Interface to FCH

- Four independent display controllers

- Seven Digital Display Interfaces

- 3 × single link, dual link DVI by combining DP1:DP0

- 3 × multiplexed with 1x4 (dual link DVI 1x8) GFX lanes

- 1 × multiplexed with GPP lanes 7:4

- DisplayPort 1.2 up to 3840 × 2160 at 30 Hz and 24 bpp, HDCP 1.1, DP++, DP audio

- eDP 1.3 up to 1920 × 1080 at 60 Hz and 30 bpp

- Single/dual link DVI up to 2560 × 1600 at 60 Hz and 30 bpp

- HDMI 1.3 up to 4096 × 2160 at 24 Hz and 24 bpp, HDCP 1.3

- VGA via FCH DP-DAC

- Seven Digital Display Interfaces

- Power Management

- AMD PowerNow! technology

- ACPI P-states, processor power states C0, C1, CC6, PC6, sleep states S0, S3, S4, S5

- PCIe power gating

- PCIe speed power policy

- SmartSleep

- AMD Turbo CORE technology with per-core power gating

- Dynamic panel refresh rate, panel self-refresh

- Thermal Controls

- Sideband temperature control

- Hardware thermal control

- DRAM thermal protection

Chipsets

- AMD FCH A76M, codename "Bolton-M3"

- AMD FCH A77E, codename "Bolton-E4"

Processors using package FP3

- AMD A-Series APU, codename "Kaveri"

- AMD Embedded R-Series APU "Bald Eagle"

| List of all FP3-based Processors | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Model | Price | Process | Launched | µarch | Family | Core | C | T | Freq | Turbo | TDP | ||||||||

| Count: 0 | |||||||||||||||||||

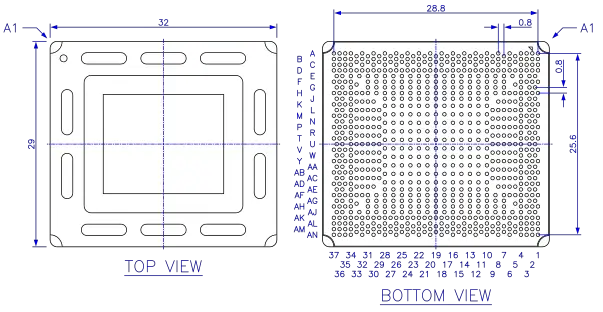

Package Diagram

Approximate dimensions of the Kaveri package. All dimensions in millimeters.

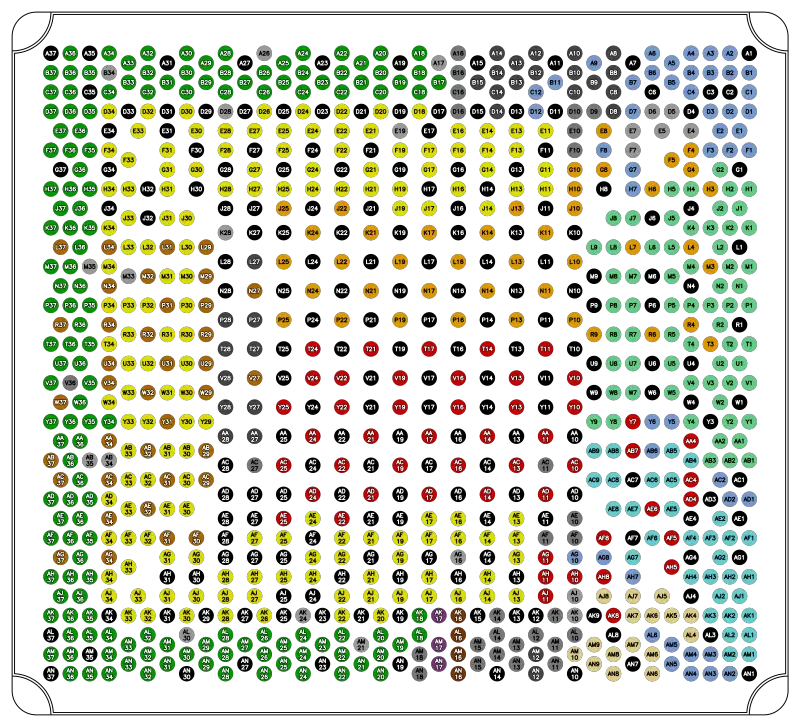

FP3 package ball numbers.

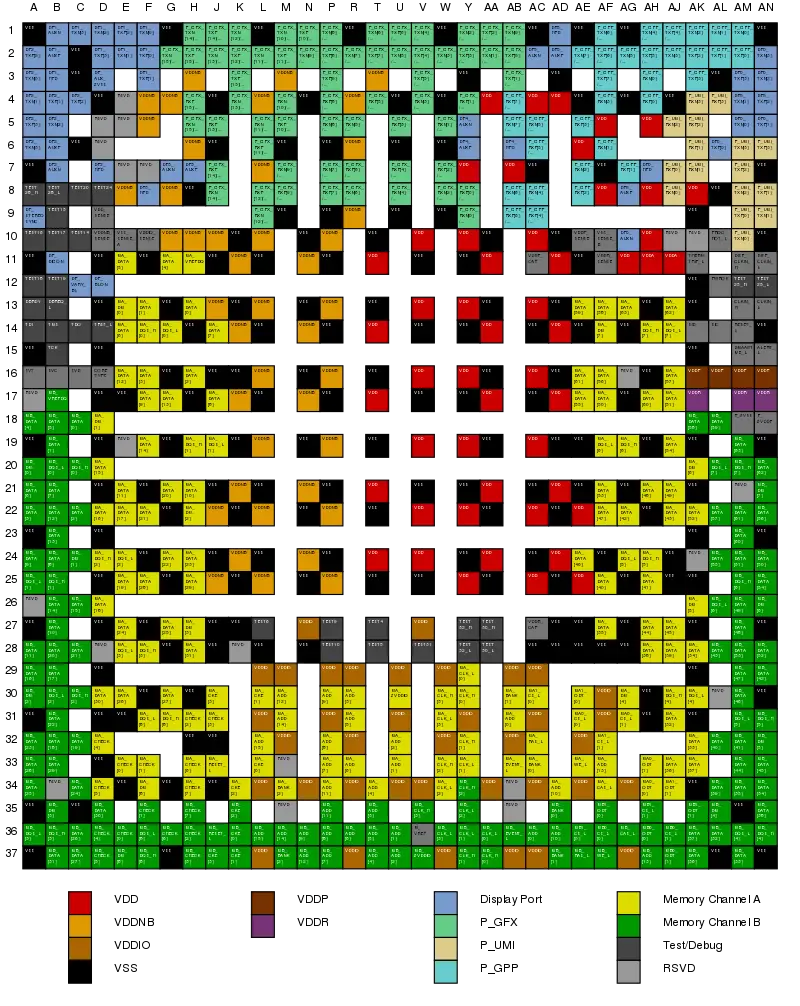

Pin Map

References

- "BIOS and Kernel Developer’s Guide (BKDG) for AMD Family 15h Models 30h-3Fh Processors", AMD Publ. #49125, Rev. 3.06, February 12, 2015

- "Revision Guide for AMD Family 15h Models 30h-3Fh Processors", AMD Publ. #51603, Rev. 1.06, April 21, 2014

- "Product Brief: 2nd Generation AMD Embedded R-Series APU", PID 1726406-A, 2017

- "White Paper: Small Form Factor Board Designs", AMD Publ. #54507, Rev. A

See also

Facts about "Package FP3 - AMD"

| designer | AMD + |

| first launched | June 2014 + |

| instance of | package + |

| market segment | Mobile + and Embedded + |

| microarchitecture | Steamroller + |

| name | Package FP3 + |

| package | BGA-854 + |

| package contacts | 854 + |

| package length | 29 mm (2.9 cm, 1.142 in) + |

| package pitch | 0.8 mm (0.0315 in) + |

| package type | Organic Micro Ball Grid Array + |

| package width | 32 mm (3.2 cm, 1.26 in) + |

| tdp | 35 W (35,000 mW, 0.0469 hp, 0.035 kW) + |