| Edit Values |

| Cortex-M55 µarch |

|

| Arch Type | CPU |

| Designer | ARM Holdings |

| Manufacturer | TSMC |

| Introduction | February 10, 2020 |

| Process | 55 nm, 45 nm, 32 nm, 28 nm, 22 nm, 16 nm, 10 nm, 7 nm, 5 nm |

| Core Configs | 1, 2, 4 |

|

| Type | Scalar, Pipelined |

| OoOE | No |

| Speculative | No |

| Reg Renaming | No |

| Stages | 4 |

| Decode | 1-2-way |

|

| ISA | ARMv8.1-M |

| Extensions | FPU, Helium |

|

| L1I Cache | 0-64 KiB/core

2-way set associative |

| L1D Cache | 0-64 KiB/core

4-way set associative |

Cortex-M55 is an ultra-low-power ARM microarchitecture designed by ARM Holdings for microcontrollers and embedded subsystems. This microarchitecture is designed as a synthesizable IP core and is sold to other semiconductor companies to be implemented in their own chips. The Cortex-M55, which implemented the ARMv8.1-M ISA, is an ultra-low-power core which is often found in microcontrllers, low-power chips, and in the embedded subsystems of more powerful chips.

History

The Cortex-M55 was officially launched on February 10, 2020. Support for custom instructions will be added in 2021.

Process Technology

Though the Cortex-M55 is designed to be fabricated on various different process nodes ranging from very mature nodes such as the 130 nm to leading-edge 7 nm and 5 nm nodes.

Compiler support

| Compiler |

Arch-Specific |

Arch-Favorable

|

| Arm Compiler |

-mcpu=cortex-m55 |

-mtune=cortex-m55

|

| GCC |

-mcpu=cortex-m55 |

-mtune=cortex-m55

|

| LLVM |

-march=cortex-m55 |

-mtune=cortex-m55

|

Architecture

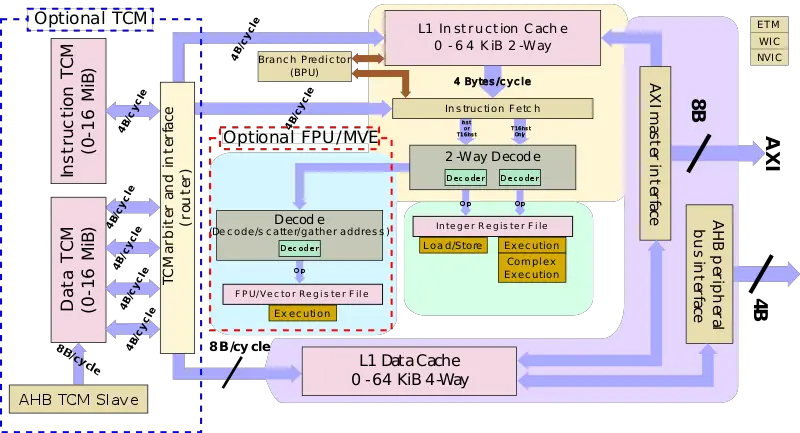

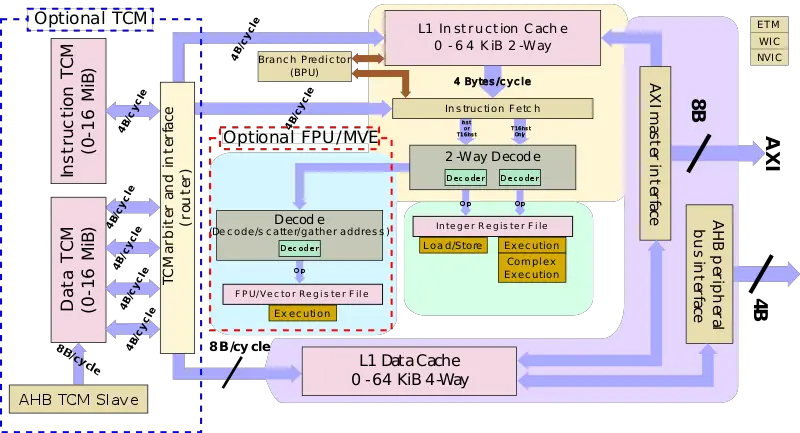

Block Diagram

Memory Hierarchy

The Cortex-M55 has a private L1I, L1D, I-TCM, and D-TCM. All four are configurable in size.

- Cache

- L1I Cache

- 0 - 64 KiB

- 2-way set associative

- Optional ECC support

- L1D Cache

- TCM

- I-TCM

- 0 - 16 MiB

- Supports wait-states

- Optional ECC support

- D-TCM

- 0 - 16 MiB

- Supports wait-states

- Optional ECC support

Overview

Pipeline

Memory subsystem

All Cortex-M55 chips

Bibliography

- Arm. personal communication. February 2020.