| Edit Values | |

| Zen+ µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | AMD |

| Manufacturer | GlobalFoundries |

| Introduction | April 2018 |

| Process | 12 nm |

| Core Configs | 2, 4, 6, 8, 12, 16 |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Stages | 19 |

| Decode | 4-way |

| Instructions | |

| ISA | x86-64 |

| Extensions | MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, AVX, AVX2, AES, PCLMUL, RDRND, F16C, BMI, BMI2, RDSEED, ADCX, PREFETCHW, CLFLUSHOPT, XSAVE, SHA, CLZERO |

| Cache | |

| L1I Cache | 64 KiB/core 4-way set associative |

| L1D Cache | 32 KiB/core 8-way set associative |

| L2 Cache | 512 KiB/core 8-way set associative |

| L3 Cache | 2 MiB/core 16-way set associative |

| Succession | |

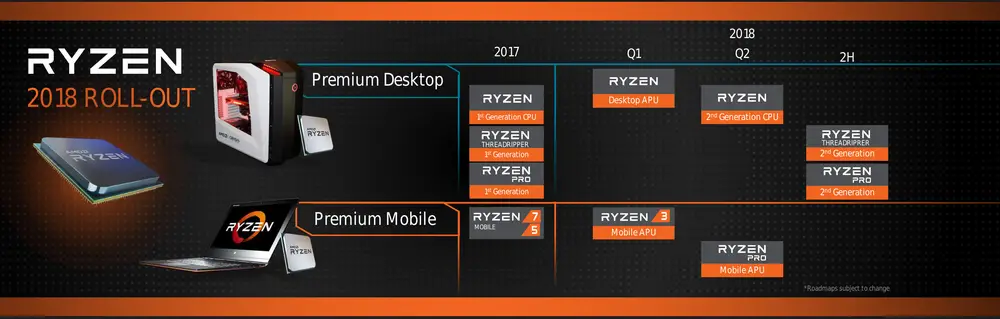

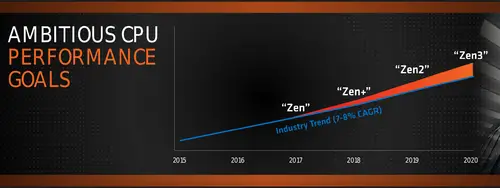

Zen+ (Zen Plus) is a planned microarchitecture being developed by AMD as a successor to Zen. Zen+ is expected to be succeeded by Zen 2.

Zen+ based processors are sold under the brand Ryzen 2nd Generation.

Contents

History

Zen+ is set to succeed Zen in April of 2018. Zen+ will feature the same core as Zen but will take advantage of the new GlobalFoundries' 12nm process to deliver higher clock speeds and improved power consumption. Zen+ was initially mentioned by AMD's senior fellow and lead architect of Zen, Michael Clark, during Hot Chips 28 in 2016 as part of AMD's continuing commitment in the high-performance computing market.

Codenames

| Core | C/T | Target |

|---|---|---|

| Pinnacle Ridge | Up to 8/16 | Mainstream to high-end desktops & enthusiasts market processors |

| Picasso | 4/8 | Mainstream desktop & mobile processors with GPU |

Release Dates

AMD intends on launching 2nd generation Ryzen in April of 2018. 2nd Generation Ryzen Threadripper and Ryzen PRO processors will launch in the second half of 2018.

Architecture

Serving as a light refresh over Zen, those processors have around ten percent higher base frequency for the same power envelope.

Key changes from Zen

- ~10% higher clock frequency

- 12 nm process (from 14 nm)

- Precision Boost 2 (from Precision Boost)

- Mainstream chipsets (See § Sockets/Platform)

- X370 → X470

- Lower Power

- Bug fixes

- OEM related issues resolved (unspecified)

- X370 → X470

Block Diagram

| This section is empty; you can help add the missing info by editing this page. |

Memory Hierarchy

| This section is empty; you can help add the missing info by editing this page. |

Sockets/Platform

| This section is empty; you can help add the missing info by editing this page. |

References

- AMD CES Tech Day 2018, Jim Anderson

- AMD CES Tech Day 2018, Lisa Su

- AMD CES Tech Day 2018, Mark Papermaster

Documents

See Also

- Intel Coffee Lake

| codename | Zen+ + |

| core count | 2 +, 4 +, 6 +, 8 +, 12 + and 16 + |

| designer | AMD + |

| first launched | April 2018 + |

| full page name | amd/microarchitectures/zen+ + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | GlobalFoundries + |

| microarchitecture type | CPU + |

| name | Zen+ + |

| pipeline stages | 19 + |

| process | 12 nm (0.012 μm, 1.2e-5 mm) + |