| Edit Values | |

| Drive Xavier | |

| General Info | |

| Designer | Nvidia |

| Manufacturer | TSMC |

| Market | Artificial Intelligence |

| Introduction | January 8, 2018 (announced) |

| General Specs | |

| Series | Drive |

| Microarchitecture | |

| ISA | ARMv8 (ARM) |

| Process | 12 nm |

| Transistors | 9,000,000,000 |

| Technology | CMOS |

| Die | 350 mm² |

| Word Size | 64 bit |

| Cores | 8 |

| Threads | 8 |

| Electrical | |

| TDP | 30 W |

| TDP (Typical) | 20 W |

Drive Xavier is a 64-bit ARM high-performance autonomous machine neural processor designed by Nvidia and introduced in 2018. The Drive Xavier is incorporated into Nvidia's Drive Pegasus autonomous computer.

Contents

Overview

The Drive Xavier is an autonomous machine system on chip designed by Nvidia and introduced at CES 2018. Silicon came back in the last week of December 2017 with sampling started in the first quarter of 2018. NVIDIA plans on mass production by the end of the year. NVIDIA reported that the product is a result of $2 billion R&D and 8,000 engineering hours. The chip is said to have full redundancy and diversity in its functional blocks. That is, the SoC can continue to operate properly even after a fault is detected.

Architecture

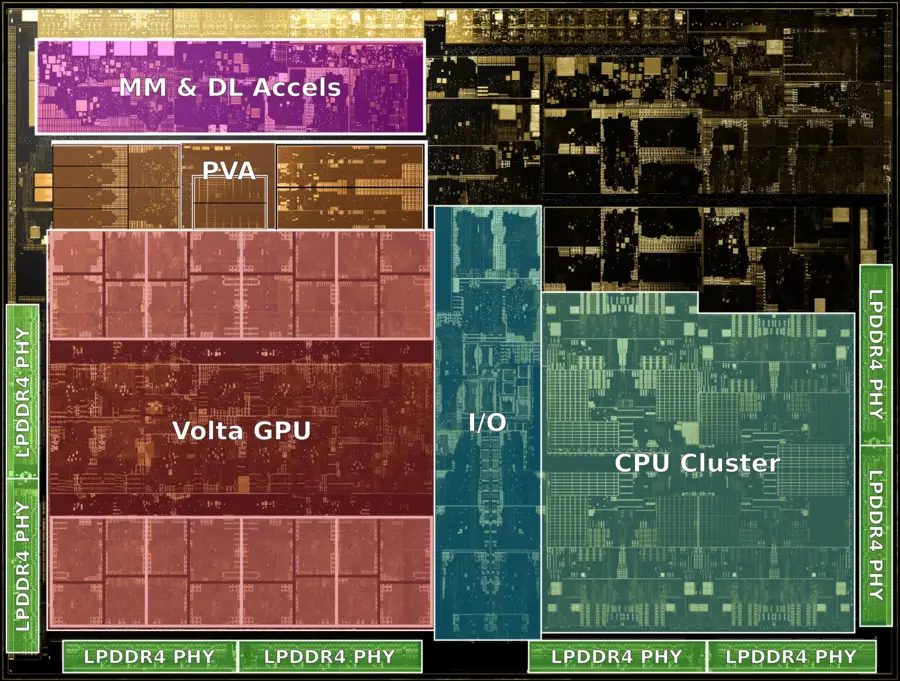

CPU

- Main article: Carmel core

The chip features eight Carmel core, Nvidia's own custom 64-bit ARM cores. Those cores have full ECC and parity as well as dual-execution (unknown if lockstep or something a bit different) allowing all code to execute twice for redundancy reasons.

GPU

- Main article: Volta

The chip incorporates a Volta GPU with 512 CUDA Cores capable of operating in 64-bit and 32-bit floating point as well as 8-bit integer. This allows the various deep learning artificial neural networks types to run efficiently in the format most suitable for them. This translates to 1.3 CUDA TOPS (32-bit FP) and another 20 Tensor Core TOPS (16-bit FP).

Accelerators

The Drive Xavier incorporates a Programmable Vision Accelerator (PVA) for processing computer vision. It is capable of 1.6 TOPS and the ability to do stereo disparity (e.g., processing parallax between two camera to obtain useful information such as depth), optical flow (e.g., direction and speed of vectors), and image processing. Additionally, since the chip is expected to be connected to a network of camera (e.g., side, front, inside), the chip is capable of doing real time encoding for all camera in high dynamic range.

| Video Processing | |

|---|---|

| Encode | Decode |

| 1.2 GPIX/s | 1.8 GPIX/s |

The chip has an ISP with native full-range HDR support and tile rendering capable of processing at 1.5 GPIX/s.

Deep Learning Accelerator

The chip incorporates a deep learning accelerator (DLA) that implements a number of specific set of deep learning functions common to many applications. This allows them to read the highest possible energy efficiency for those operations. The DLA has a peak performance of 5 TOPS for 16-bit integers or 10 TOPS for 8-bit integer.

Memory controller

|

Integrated Memory Controller

|

||||||||||

|

||||||||||

I/O

- 16 CSI channels

- 109 Gbps total bandwidth

- 1x gE interface

- 1x 10gE interface

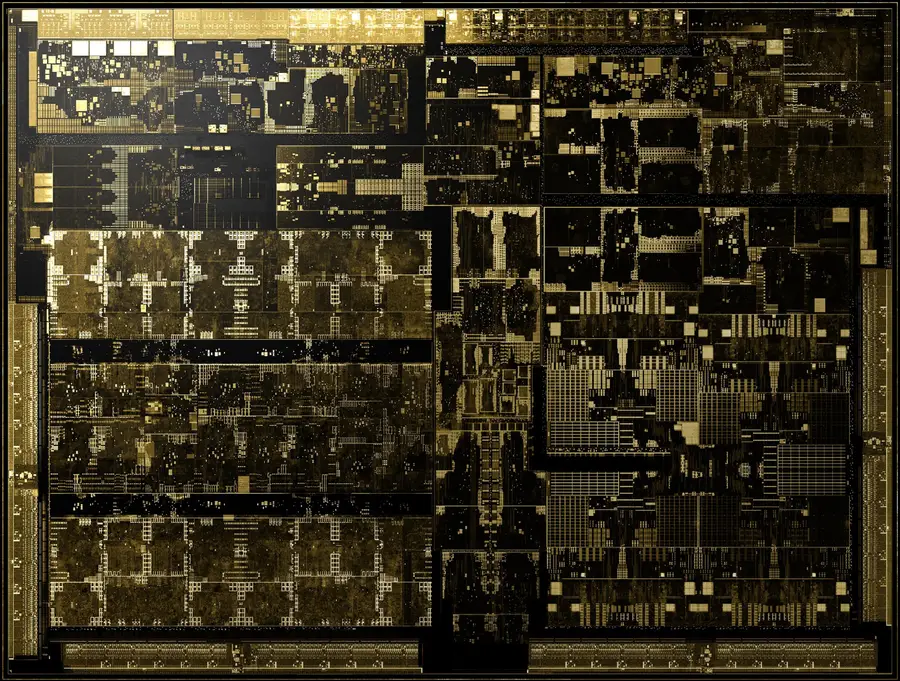

Die

| core count | 8 + |

| designer | Nvidia + |

| die area | 350 mm² (0.543 in², 3.5 cm², 350,000,000 µm²) + |

| first announced | January 8, 2018 + |

| full page name | nvidia/tegra/xavier + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| isa | ARMv8 + |

| isa family | ARM + |

| ldate | 3000 + |

| manufacturer | TSMC + |

| market segment | Artificial Intelligence + |

| max memory bandwidth | 127.1 GiB/s (130,150.4 MiB/s, 136.473 GB/s, 136,472.586 MB/s, 0.124 TiB/s, 0.136 TB/s) + |

| max memory channels | 8 + |

| name | Drive Xavier + |

| process | 12 nm (0.012 μm, 1.2e-5 mm) + |

| series | Drive + |

| supported memory type | LPDDR4-2133 + |

| tdp | 30 W (30,000 mW, 0.0402 hp, 0.03 kW) + |

| tdp (typical) | 20 W (20,000 mW, 0.0268 hp, 0.02 kW) + |

| technology | CMOS + |

| thread count | 8 + |

| transistor count | 9,000,000,000 + |

| word size | 64 bit (8 octets, 16 nibbles) + |