From WikiChip

Search results

Page title matches

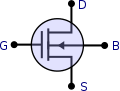

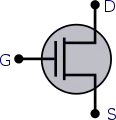

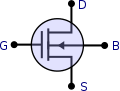

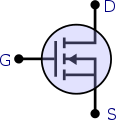

File:Nmos,dep,body.svg |description={{en|1=NMOS, depletion mode, with bulk.}}(130 × 135 (8 KB)) - 02:54, 22 March 2014

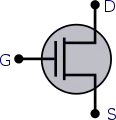

File:Nmos,dep,body2.svg |description={{en|1=NMOS, depletion mode, with bulk.}}(179 × 135 (9 KB)) - 02:54, 22 March 2014

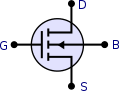

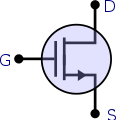

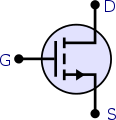

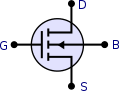

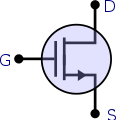

File:Nmos,en,body,2.svg |description={{en|1=NMOS, enhancement mode, with bulk.}}(179 × 135 (9 KB)) - 02:54, 22 March 2014

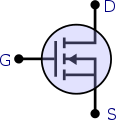

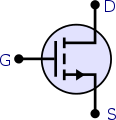

File:Nmos,en,body.svg |description={{en|1=NMOS, enhancement mode, with bulk.}}(130 × 135 (8 KB)) - 02:54, 22 March 2014

File:Nmos,en,2.svg |description={{en|1=NMOS, enhancement mode, without bulk.}}(130 × 135 (7 KB)) - 02:54, 22 March 2014

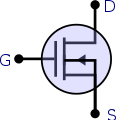

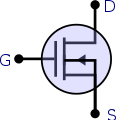

File:Nmos,dep.svg |description={{en|1=NMOS, depletion mode, without bulk.}}(130 × 135 (8 KB)) - 02:55, 22 March 2014

File:Nmos,en.svg |description={{en|1=NMOS, enhancement mode, without bulk.}}(130 × 135 (8 KB)) - 02:55, 22 March 2014

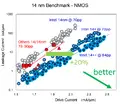

File:intel 14nm++ (nmos).png [[Intel]]'s [[14 nm|14 nm ++]] process [[nMOS]] transistor performance. By Intel.(711 × 615 (143 KB)) - 05:18, 4 April 2017

File:intel 14nm+ (nmos).png [[Intel]]'s [[14 nm|14 nm +]] process [[nMOS]] transistor performance. By Intel.(714 × 619 (116 KB)) - 05:01, 4 April 2017-

382 bytes (55 words) - 05:02, 4 April 2017

Page text matches

- | nMOS/pMOS || depletion-mode nMOS || nMOS/pMOS/CMOS ||1 KB (119 words) - 23:04, 20 May 2018

- | HMOS-II || HMOS-E || P646 (CHMOS III) || NMOS III || || CMOS-2 ! colspan="3" | [[HP]] NMOS-III Design Rules3 KB (332 words) - 23:04, 20 May 2018

- | nMOS || CMOS || CMOS || BiCMOS1 KB (166 words) - 23:04, 20 May 2018

- | tech = nMOS ...designed by [[Toshiba]] during the late 1970s. The [[microprocessor]] uses nMOS technology and was primarily used in printers and displays.1 KB (119 words) - 14:45, 3 February 2016

- ...d became the first truly widely used DRAM chip. Those chips used Si-gate [[nMOS]] transistors using a polysilicon word line and an aluminum metal bit line. | fab 1 xtor.tech = nMOS, pMOS5 KB (632 words) - 23:04, 20 May 2018

- * pull-down network (PDN) - a set of [[NMOS]] transistors connected between GND and the output line1 KB (221 words) - 18:07, 26 November 2018

- [[File:Nmos.svg|thumb|right|[[n-type semiconductor]].]] An '''nMOS transistor''' is built with a p-type body with two regions of n-type semico8 KB (1,362 words) - 23:38, 17 November 2015

File:Nmos,dep,body.svg |description={{en|1=NMOS, depletion mode, with bulk.}}(130 × 135 (8 KB)) - 02:54, 22 March 2014

File:Nmos,dep,body2.svg |description={{en|1=NMOS, depletion mode, with bulk.}}(179 × 135 (9 KB)) - 02:54, 22 March 2014

File:Nmos,en,body,2.svg |description={{en|1=NMOS, enhancement mode, with bulk.}}(179 × 135 (9 KB)) - 02:54, 22 March 2014

File:Nmos,en,body.svg |description={{en|1=NMOS, enhancement mode, with bulk.}}(130 × 135 (8 KB)) - 02:54, 22 March 2014

File:Nmos,en,2.svg |description={{en|1=NMOS, enhancement mode, without bulk.}}(130 × 135 (7 KB)) - 02:54, 22 March 2014

File:Nmos,dep.svg |description={{en|1=NMOS, depletion mode, without bulk.}}(130 × 135 (8 KB)) - 02:55, 22 March 2014

File:Nmos,en.svg |description={{en|1=NMOS, enhancement mode, without bulk.}}(130 × 135 (8 KB)) - 02:55, 22 March 2014- ...to HIGH as it's connected to VDD but not GND. When the input is HIGH, the nMOS transistor is on and the pMOS transistor is off yielding an output that is ...e \( i_{DP} = i_{DN} = 0 \). When the input is LOW, pMOS is conducting and nMOS is off; the load capacitor is charged via the pMOS device.The power dissipa6 KB (983 words) - 04:50, 8 November 2015

- | tech = nMOS2 KB (244 words) - 00:33, 19 May 2016

- | tech = nMOS1 KB (140 words) - 05:28, 22 January 2016

- | tech 2 = nMOS ...instructions with a 10 microsecond instruction cycle. The chips come in [[nMOS]], [[pMOS]], and [[CMOS]] versions.4 KB (462 words) - 19:14, 13 October 2019

- | tech 2 = nMOS | {{matsushita|MN1542}} || 2048x8 ROM, 152x4 RAM, 28 I/O || NMOS ||3 KB (301 words) - 19:23, 13 October 2019

- ...]], the 10800 series was designed for very high speed applications where [[nMOS]] components were insufficient.2 KB (179 words) - 00:03, 3 February 2016