|

|

| Line 1: |

Line 1: |

| − | {{amd title|Rome|core}}

| |

| − | {{core

| |

| − | |name=Rome

| |

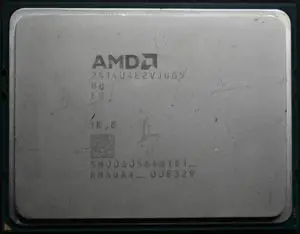

| − | |image=amd rome (front).jpg

| |

| − | |caption=Package front

| |

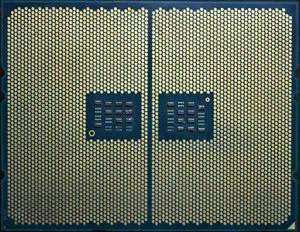

| − | |back image=amd rome (back).jpg

| |

| − | |back image size=Package back

| |

| − | |developer=AMD

| |

| − | |manufacturer=TSMC

| |

| − | |manufacturer 2=GlobalFoundries

| |

| − | |first announced=May 16, 2017

| |

| − | |first launched=August 7, 2019

| |

| − | |isa=x86-64

| |

| − | |isa family=x86

| |

| − | |microarch=Zen 2

| |

| − | |word=64 bit

| |

| − | |proc=7 nm

| |

| − | |tech=CMOS

| |

| − | |package name 1=amd,socket_sp3

| |

| − | |predecessor=Naples

| |

| − | |predecessor link=amd/cores/naples

| |

| − | |successor=Milan

| |

| − | |successor link=amd/cores/milan

| |

| − | |proc 2=14 nm

| |

| − | }}

| |

| − | '''Rome''' is codename for [[AMD]]'s high-performance server microprocessors based on the {{amd|Zen 2|l=arch}} microarchitecture serving as a successor to {{\\|Naples}}.

| |

| | | | |

| − | Rome-based microprocessors are branded as second-generation, {{amd|EPYC#7002 Series (Zen 2)|7002-series}}, {{amd|EPYC|EPYC processors}}.

| |

| − |

| |

| − | [[File:amd epyc rodmap.png|right|thumb|AMD datacenter roadmap]]

| |

| − |

| |

| − | == Overview ==

| |

| − | AMD Rome [[system on chips]] are a series of high-performance [[multiprocessors]] designed by [[AMD]] based on their {{amd|Zen 2|l=arch}} microarchitecture. Rome-based logic chips are fabricated on TSMC [[7 nm process]] with the i/o components made on GlobalFoundries [[14 nm process]]. Rome SoCs support both single and 2-way multiprocessing with up to a maximum of 64 cores (and 128 threads) per processor for a total of up to 128 cores (and 256 threads) for a 2-way MP system. Those SoCs support 128 PCIe lanes each. When in a two-socket configuration, a total of 160 PCIe lanes can be provided at the platform level by both chips. Rome is backward platform/socket (Socket SP3) compatible with {{\\|Naples}} and forward-compatible with {{\\|Milan}}.

| |

| − |

| |

| − | === Common Features ===

| |

| − | All Rome processors have the following:

| |

| − | * 128 PCIe lanes (in both single-way and dual-way multiprocessing)

| |

| − | ** PCIe Gen 4

| |

| − | * Octa-channel Memory

| |

| − | ** Up to DDR4-3200 ECC

| |

| − | ** Up to 4 [[TiB]]

| |

| − | *** Up to 16 x 256 GiB @ 1.2 V

| |

| − | *** RDIMM/LRDIMM/3DS/NVDIMM

| |

| − | * Up to 64 cores / 128 threads

| |

| − | * Everything up to {{x86||AVX2}} (i.e., {{x86|SMM}}, {{x86|FPU}}, {{x86|NX}}, {{x86|MMX}}, {{x86|SSE}}, {{x86|SSE2}}, {{x86|SSE3}}, {{x86|SSSE3}}, {{x86|SSE4.1}}, {{x86|SSE4.2}}, {{x86|AES}}, {{x86|AVX}}, {{x86|FMA3}}, and {{x86|AVX2}}), and {{x86|SHA}}

| |

| − |

| |

| − | {{clear}}

| |

| − |

| |

| − | == Rome Processors ==

| |

| − | <!-- NOTE:

| |

| − | This table is generated automatically from the data in the actual articles.

| |

| − | If a microprocessor is missing from the list, an appropriate article for it needs to be

| |

| − | created and tagged accordingly.

| |

| − |

| |

| − | Missing a chip? please dump its name here: https://en.wikichip.org/wiki/WikiChip:wanted_chips

| |

| − | -->

| |

| − | {{comp table start}}

| |

| − | <table class="comptable sortable tc5 tc6">

| |

| − | {{comp table header|main|10:List of Rome Processors}}

| |

| − | {{comp table header|cols|Family|Price|Launched|Cores|Threads|TDP|L2$|L3$|Base|Turbo}}

| |

| − | {{comp table header|lsep|25:[[Uniprocessors]]}}

| |

| − | {{#ask: [[Category:microprocessor models by amd]] [[core name::Rome]] [[max cpu count::1]]

| |

| − | |?full page name

| |

| − | |?model number

| |

| − | |?microprocessor family

| |

| − | |?release price

| |

| − | |?first launched

| |

| − | |?core count

| |

| − | |?thread count

| |

| − | |?tdp

| |

| − | |?l2$ size

| |

| − | |?l3$ size

| |

| − | |?base frequency#GHz

| |

| − | |?turbo frequency#GHz

| |

| − | |format=template

| |

| − | |template=proc table 3

| |

| − | |userparam=12

| |

| − | |mainlabel=-

| |

| − | |valuesep=,

| |

| − | }}

| |

| − | {{comp table header|lsep|25:[[Multiprocessors]] (dual-socket)}}

| |

| − | {{#ask: [[Category:microprocessor models by amd]] [[core name::Rome]] [[max cpu count::>>1]]

| |

| − | |?full page name

| |

| − | |?model number

| |

| − | |?microprocessor family

| |

| − | |?release price

| |

| − | |?first launched

| |

| − | |?core count

| |

| − | |?thread count

| |

| − | |?tdp

| |

| − | |?l2$ size

| |

| − | |?l3$ size

| |

| − | |?base frequency#GHz

| |

| − | |?turbo frequency#GHz

| |

| − | |format=template

| |

| − | |template=proc table 3

| |

| − | |userparam=12

| |

| − | |mainlabel=-

| |

| − | |valuesep=,

| |

| − | }}

| |

| − | {{comp table count|ask=[[Category:microprocessor models by amd]] [[core name::Rome]]}}

| |

| − | </table>

| |

| − | {{comp table end}}

| |

| − |

| |

| − | === SKU Comparison ===

| |

| − | Below are a number of SKU comparison graphs based on their specifications.

| |

| − |

| |

| − | <div style="float: left; margin: 10px">

| |

| − | {{#ask: [[Category:microprocessor models by amd]] [[core name::Rome]]

| |

| − | |?core count

| |

| − | |?base frequency

| |

| − | |charttitle=Cores vs. Base Frequency

| |

| − | |numbersaxislabel=Frequency (MHz)

| |

| − | |labelaxislabel=Core Count

| |

| − | |height=400

| |

| − | |width=400

| |

| − | |theme=vector

| |

| − | |group=property

| |

| − | |grouplabel=subject

| |

| − | |charttype=scatter

| |

| − | |format=jqplotseries

| |

| − | |mainlabel=-

| |

| − | }}

| |

| − | </div>

| |

| − |

| |

| − | <div style="float: left; margin: 10px">

| |

| − | {{#ask: [[Category:microprocessor models by amd]] [[core name::Rome]]

| |

| − | |?core count

| |

| − | |?turbo frequency

| |

| − | |charttitle=Cores vs. Turbo Frequency

| |

| − | |numbersaxislabel=Frequency (MHz)

| |

| − | |labelaxislabel=Core Count

| |

| − | |height=400

| |

| − | |width=400

| |

| − | |theme=vector

| |

| − | |group=property

| |

| − | |grouplabel=subject

| |

| − | |charttype=scatter

| |

| − | |format=jqplotseries

| |

| − | |mainlabel=-

| |

| − | }}

| |

| − | </div>

| |

| − |

| |

| − | <div style="float: left; margin: 10px">

| |

| − | {{#ask: [[Category:microprocessor models by amd]] [[core name::Rome]]

| |

| − | |?core count

| |

| − | |?tdp

| |

| − | |charttitle=Cores vs. TDP

| |

| − | |numbersaxislabel=TDP (W)

| |

| − | |labelaxislabel=Core Count

| |

| − | |height=400

| |

| − | |width=400

| |

| − | |theme=vector

| |

| − | |group=property

| |

| − | |grouplabel=subject

| |

| − | |charttype=scatter

| |

| − | |format=jqplotseries

| |

| − | |mainlabel=-

| |

| − | }}

| |

| − | </div>

| |

| − |

| |

| − | <div style="float: left; margin: 10px">

| |

| − | {{#ask: [[Category:microprocessor models by amd]] [[core name::Rome]]

| |

| − | |?turbo frequency

| |

| − | |?tdp

| |

| − | |charttitle=Frequency vs. TDP

| |

| − | |numbersaxislabel=TDP (W)

| |

| − | |labelaxislabel=Frequency (MHz)

| |

| − | |height=400

| |

| − | |width=400

| |

| − | |theme=vector

| |

| − | |group=property

| |

| − | |grouplabel=subject

| |

| − | |charttype=scatter

| |

| − | |format=jqplotseries

| |

| − | |mainlabel=-

| |

| − | }}

| |

| − | </div>

| |

| − |

| |

| − | {{clear}}

| |

| − |

| |

| − | == See also ==

| |

| − | {{amd zen 2 core see also}}

| |

+

+ +

+