| Line 57: | Line 57: | ||

== Architecture == | == Architecture == | ||

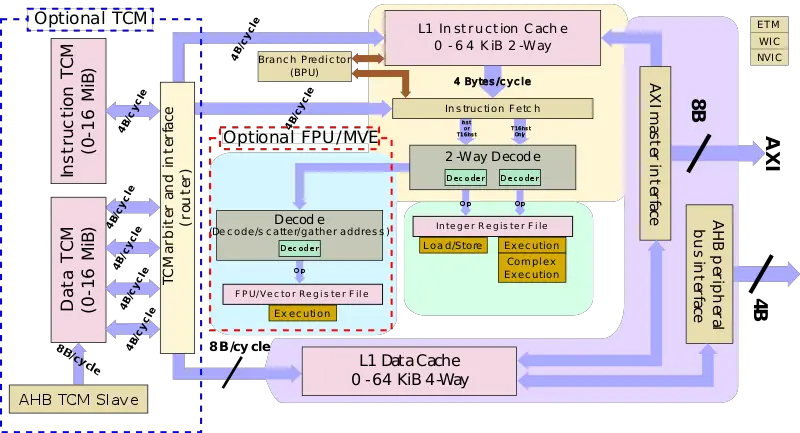

| − | == Block Diagram === | + | === Block Diagram === |

| − | :[[File:cortex-m55 block diagram.svg| | + | :[[File:cortex-m55 block diagram.svg|800px]] |

=== Memory Hierarchy === | === Memory Hierarchy === | ||

| Line 82: | Line 82: | ||

*** Supports wait-states | *** Supports wait-states | ||

*** Optional ECC support | *** Optional ECC support | ||

| + | |||

| + | == Overview == | ||

| + | {{empty section}} | ||

| + | |||

| + | === Pipeline === | ||

| + | {{empty section}} | ||

| + | |||

| + | === Memory subsystem === | ||

| + | {{empty section}} | ||

| + | |||

| + | == All Cortex-M55 chips == | ||

| + | <!-- NOTE: | ||

| + | This table is generated automatically from the data in the actual articles. | ||

| + | If a microprocessor is missing from the list, an appropriate article for it needs to be | ||

| + | created and tagged accordingly. | ||

| + | |||

| + | Missing a chip? please dump its name here: https://en.wikichip.org/wiki/WikiChip:wanted_chips | ||

| + | --> | ||

| + | {{comp table start}} | ||

| + | <table class="comptable sortable"> | ||

| + | {{comp table header|main|4:List of Cortex-M55-based Processors}} | ||

| + | {{comp table header|cols|Launched|Cores|%Frequency}} | ||

| + | {{#ask: [[Category:microprocessor models by arm holdings]] [[microarchitecture::Cortex-M55]] | ||

| + | |?full page name | ||

| + | |?model number | ||

| + | |?first launched | ||

| + | |?core count | ||

| + | |?base frequency#GHz | ||

| + | |format=template | ||

| + | |template=proc table 3 | ||

| + | |userparam=5 | ||

| + | |mainlabel=- | ||

| + | }} | ||

| + | {{comp table count|ask=[[Category:microprocessor models by arm holdings]] [[microarchitecture::Cortex-M55]]}} | ||

| + | </table> | ||

| + | {{comp table end}} | ||

| + | |||

| + | == Bibliography == | ||

| + | * {{bib|personal|February 2020|Arm}} | ||

Revision as of 00:57, 16 February 2020

| Edit Values | |

| Cortex-M55 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | ARM Holdings |

| Manufacturer | TSMC |

| Introduction | February 10, 2020 |

| Process | 55 nm, 45 nm, 32 nm, 28 nm, 22 nm, 16 nm, 10 nm, 7 nm, 5 nm |

| Core Configs | 1, 2, 4 |

| Pipeline | |

| Type | Scalar, Pipelined |

| OoOE | No |

| Speculative | No |

| Reg Renaming | No |

| Stages | 4 |

| Decode | 1-2-way |

| Instructions | |

| ISA | ARMv8.1-M |

| Extensions | FPU, Helium |

| Cache | |

| L1I Cache | 0-64 KiB/core 2-way set associative |

| L1D Cache | 0-64 KiB/core 4-way set associative |

Cortex-M55 is an ultra-low-power ARM microarchitecture designed by ARM Holdings for microcontrollers and embedded subsystems. This microarchitecture is designed as a synthesizable IP core and is sold to other semiconductor companies to be implemented in their own chips. The Cortex-M55, which implemented the ARMv8.1-M ISA, is an ultra-low-power core which is often found in microcontrllers, low-power chips, and in the embedded subsystems of more powerful chips.

Contents

History

The Cortex-M55 was officially launched on February 10, 2020. Support for custom instructions will be added in 2021.

Process Technology

Though the Cortex-M55 is designed to be fabricated on various different process nodes ranging from very mature nodes such as the 130 nm to leading-edge 7 nm and 5 nm nodes.

Compiler support

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| Arm Compiler | -mcpu=cortex-m55 |

-mtune=cortex-m55

|

| GCC | -mcpu=cortex-m55 |

-mtune=cortex-m55

|

| LLVM | -march=cortex-m55 |

-mtune=cortex-m55

|

Architecture

Block Diagram

Memory Hierarchy

The Cortex-M55 has a private L1I, L1D, I-TCM, and D-TCM. All four are configurable in size.

- Cache

- L1I Cache

- 0 - 64 KiB

- 2-way set associative

- Optional ECC support

- L1D Cache

- 0 - 64 KiB

- 4-way set associative

- Supports both write-back (WB) and write-through (WT)

- Optional ECC support

- L1I Cache

- TCM

- I-TCM

- 0 - 16 MiB

- Supports wait-states

- Optional ECC support

- D-TCM

- 0 - 16 MiB

- Supports wait-states

- Optional ECC support

- I-TCM

Overview

| This section is empty; you can help add the missing info by editing this page. |

Pipeline

| This section is empty; you can help add the missing info by editing this page. |

Memory subsystem

| This section is empty; you can help add the missing info by editing this page. |

All Cortex-M55 chips

| List of Cortex-M55-based Processors | ||||

|---|---|---|---|---|

| Model | Launched | Cores | Frequency | |

| Count: 0 | ||||

Bibliography

- Arm. personal communication. February 2020.

| codename | Cortex-M55 + |

| core count | 1 +, 2 + and 4 + |

| designer | ARM Holdings + |

| first launched | February 10, 2020 + |

| full page name | arm holdings/microarchitectures/cortex-m55 + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8.1-M + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Cortex-M55 + |

| pipeline stages | 4 + |

| process | 55 nm (0.055 μm, 5.5e-5 mm) +, 45 nm (0.045 μm, 4.5e-5 mm) +, 32 nm (0.032 μm, 3.2e-5 mm) +, 28 nm (0.028 μm, 2.8e-5 mm) +, 22 nm (0.022 μm, 2.2e-5 mm) +, 16 nm (0.016 μm, 1.6e-5 mm) +, 10 nm (0.01 μm, 1.0e-5 mm) +, 7 nm (0.007 μm, 7.0e-6 mm) + and 5 nm (0.005 μm, 5.0e-6 mm) + |