From WikiChip

Difference between revisions of "arm holdings/microarchitectures/cortex-a8"

(→Block Diagram) |

(→Licensees) |

||

| Line 84: | Line 84: | ||

| | | | ||

* [[Broadcom]] | * [[Broadcom]] | ||

| − | |||

* [[Freescale]] | * [[Freescale]] | ||

* [[Panasonic]] | * [[Panasonic]] | ||

* [[Samsung]] | * [[Samsung]] | ||

| − | |||

* [[STMicroelectronics]] | * [[STMicroelectronics]] | ||

| − | * [[Texas | + | * [[Texas Instruments]] |

| − | |||

* [[PMC-Sierra]] | * [[PMC-Sierra]] | ||

* [[ZiiLABS]] | * [[ZiiLABS]] | ||

Revision as of 00:14, 31 December 2018

| Edit Values | |

| Cortex-A8 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | ARM Holdings |

| Manufacturer | TSMC |

| Introduction | October 5, 2005 |

| Process | 65 nm, 45 nm |

| Pipeline | |

| Type | Superscalar, Pipelined |

| OoOE | No |

| Speculative | Yes |

| Stages | 13 |

| Decode | 2-way |

| Instructions | |

| ISA | ARMv7 |

| Extensions | NEON, TrustZone, Thumb-2, Jazelle-RCT, VFPv3 |

| Succession | |

Cortex-A8 (codename Tiger) is the successor to the ARM11, a low-power performance ARM microarchitecture designed by ARM Holdings for the mobile market. This microarchitecture is designed as an IP core and is sold to other semiconductor companies to be implemented in their own chips. The Cortex-A8 was designed by the Arm Austin design center.

Contents

Architecture

The Cortex-A8 was the first application processor from the Cortex family. It is also Arm's first superscalar, dual-issue microprocessor.

Key changes from ARM11

- 65 nm process (from 90 nm)

- ARMv7 (from ARMv6)

- Support for NEON (ASIMD)

- TrustZone

- Thumb-2

- Jazelle-RCT (Realtime Compilation Target)

- ARM reported 2.0 DMIPS/MHz (up from 1.2 DMIPS/MHz)

- Average IPC reported is 0.9 (based on SPECint95, EEMBC, Mediabench, and others)

- First superscalar design

- dual-issue (from single-issue)

- in-order

- 13-stage pipeline (up from 8 stages)

- Targets frequency up to 1 GHz

- First NEON implementation

- 10-stage pipeline

- Dedicated private L2 cache

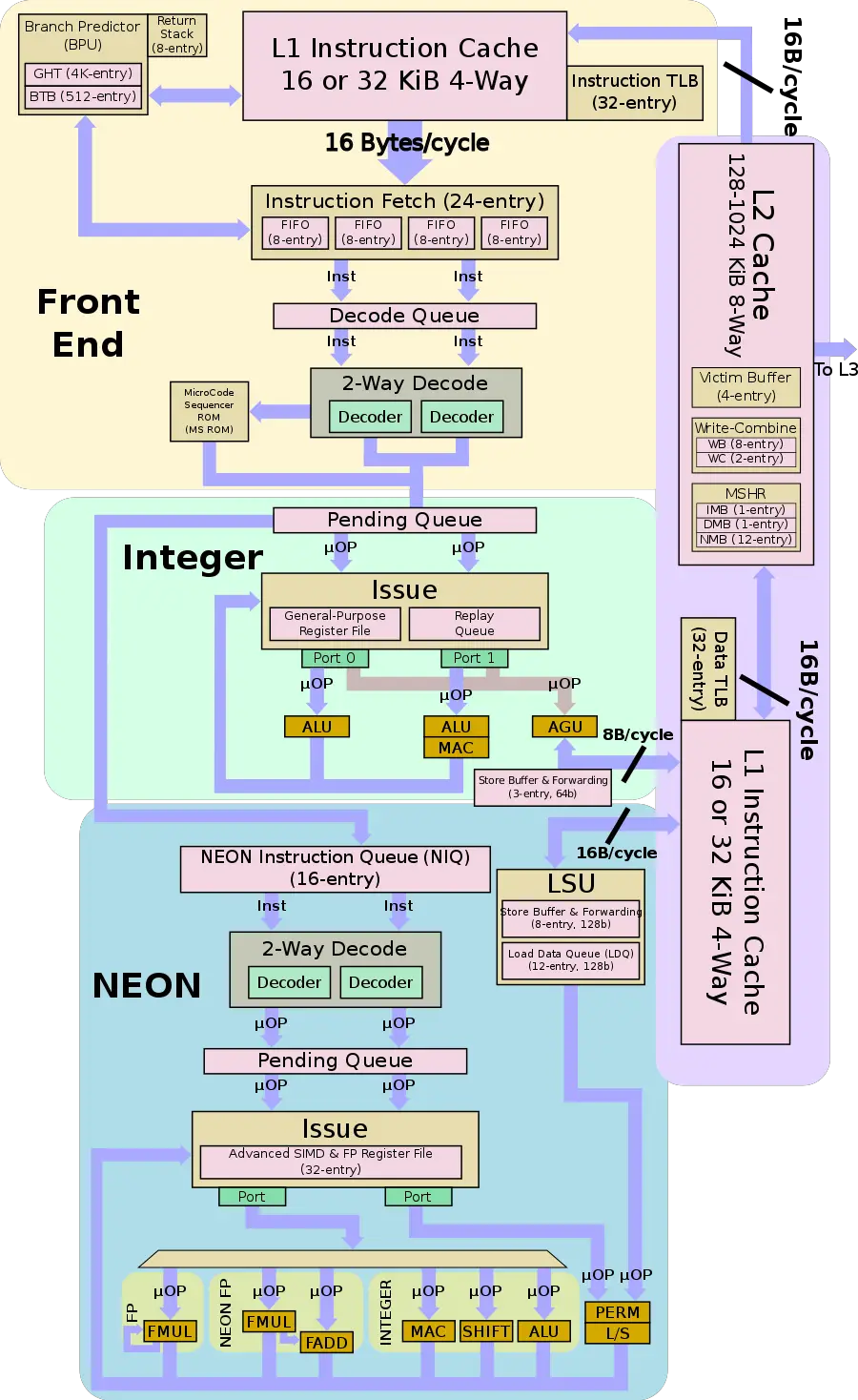

Block Diagram

Memory Hierarchy

- Cache

- L1I Cache

- 16 KiB OR 32 KiB (configurable)

- 4-way set associative

- 64 B line size

- Random replacement policy

- L1D Cache

- 16 KiB OR 32 KiB (configurable)

- 4-way set associative

- 64 B line size

- Random replacement policy

- L2 Cache

- 0 KiB OR 128 KiB OR 1 MiB (configurable)

- 8-way set associative

- 64 B line size

- Optional Parity and ECC

- L1I Cache

- TLB

- ITLB

- 32-entry, fully-associative

- 4 KiB, 64 KiB, 1 MiB, and 16 MiB page sizes

- DTLB

- 32-entry, fully-associative

- 4 KiB, 64 KiB, 1 MiB, and 16 MiB page sizes

- ITLB

Licensees

Arm named the following companies as licensees.

Die

- 65 nm process

- Up to 1 GHz

- 4 mm² (core only, no NEON, L2 cache, and embedded trace)

- <= 300 mW

Facts about "Cortex-A8 - Microarchitectures - ARM"

| codename | Cortex-A8 + |

| designer | ARM Holdings + |

| first launched | October 5, 2005 + |

| full page name | arm holdings/microarchitectures/cortex-a8 + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv7 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Cortex-A8 + |

| pipeline stages | 13 + |

| process | 65 nm (0.065 μm, 6.5e-5 mm) + and 45 nm (0.045 μm, 4.5e-5 mm) + |