(→Key changes from {{\\|Kaby Lake}}) |

(→Key changes from {{\\|Kaby Lake}}) |

||

| Line 65: | Line 65: | ||

=== Key changes from {{\\|Kaby Lake}} === | === Key changes from {{\\|Kaby Lake}} === | ||

* [[10 nm process]] (from [[14 nm]]) | * [[10 nm process]] (from [[14 nm]]) | ||

| + | * {{intel|Gen9.5|l=arch}} → {{intel|Gen10|l=arch}} graphics | ||

* Mainstream chipset | * Mainstream chipset | ||

** {{intel|Union Point|200 Series chipset|l=chipset}} → 300 Series chipset | ** {{intel|Union Point|200 Series chipset|l=chipset}} → 300 Series chipset | ||

Revision as of 11:33, 16 April 2017

| Edit Values | |

| Cannonlake µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | 2017 |

| Process | 10 nm |

| Cores | |

| Core Names | Cannonlake Y, Cannonlake U |

| Succession | |

Cannonlake (CNL) (formerly Skymont) is a planned microarchitecture by Intel as a successor to Kaby Lake. Cannonlake is expected to be fabricated using a 10 nm process and is set to be introduced in the fourth quarter of 2017. Cannonlake is the "Process" microarchitecture as part of Intel's PAO model.

For desktop and mobile, Cannonlake is expected to be branded as 8th Generation Intel Core i3, Core i5. and Core i7 processors. For server class processors, Intel is expected to brand it as Xeon E3 v7, Xeon E5 v7, and Xeon E7 v7.

Contents

Process Technology

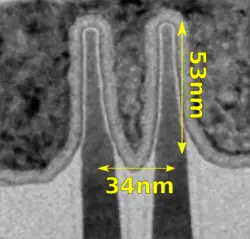

Cannonlake is manufactured on Intel's 10 nm process (P1274). Intel's 10 nm process is the first high-volume manufacturing process to employ Self-Aligned Quad Patterning (SAQP) (goes under the "Hyper-Scaling" marketing name). Intel's 10nm features a 0.0367 µm² SRAM bit cell.

| Broadwell | Cannonlake | Δ |

| |

|---|---|---|---|---|

| 14 nm | 10 nm | |||

| Fin Pitch | 42 nm | 34 | 0.81x | |

| Fin Width | 8 nm | ? nm | ?x | |

| Fin Height | 42 nm | 53 nm | 1.24x | |

| Gate Pitch | 70 nm | 54 nm | 0.77x | |

| Interconnect Pitch | 52 nm | 36 nm | 0.69x | |

| Cell Height | 399 nm | 272 nm | 0.68x |

Codenames

| Core | Abbrev | Description | Graphics | Target |

|---|---|---|---|---|

| Cannonlake Y | CNL-Y | Extremely low power | GT2 | 2-in-1s detachable, tablets, and computer sticks |

| Cannonlake U | CNL-U | Ultra-low Power | GT2 | Light notebooks, portable All-in-Ones (AiOs), Minis, and conference room |

Architecture

| This section is empty; you can help add the missing info by editing this page. |

Key changes from Kaby Lake

- 10 nm process (from 14 nm)

- Gen9.5 → Gen10 graphics

- Mainstream chipset

- 200 Series chipset → 300 Series chipset

- Integrated USB 3.1 (10 Gib/s)

- Integrated wireless controller (IEEE 802.11ac)

- 200 Series chipset → 300 Series chipset

All Cannonlake Chips

| Cannonlake Chips | |||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Main processor | IGP | Major Feature Diff | |||||||||||||||||||||

| Model | Launched | Price | Family | Platform | Core | C | T | L3$ | L4$ | TDP | Freq | Turbo | Max Mem | Name | Freq | Turbo | TBT | HT | AVX2 | TXT | TSX | vPro | VT-d |

| Uniprocessors | |||||||||||||||||||||||

| No Cannonlake Chips have been released yet. | |||||||||||||||||||||||

| Count: 0 | |||||||||||||||||||||||

See also

- AMD's Zen

| codename | Cannonlake + |

| designer | Intel + |

| first launched | 2017 + |

| full page name | intel/microarchitectures/cannon lake + |

| instance of | microarchitecture + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Cannonlake + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |