-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

Difference between revisions of "fujitsu/sparc64/sparc64 xii"

| Line 105: | Line 105: | ||

}} | }} | ||

'''SPARC64 XII''' is a high-performance {{arch|64}} [[dodeca-core]] [[SPARC]] microprocessor designed by [[Fujitsu]] and introduced in April [[2017]]. | '''SPARC64 XII''' is a high-performance {{arch|64}} [[dodeca-core]] [[SPARC]] microprocessor designed by [[Fujitsu]] and introduced in April [[2017]]. | ||

| + | |||

| + | == Cache == | ||

| + | {{empty section}} | ||

| + | |||

| + | == Expansions == | ||

| + | {{empty section}} | ||

| + | |||

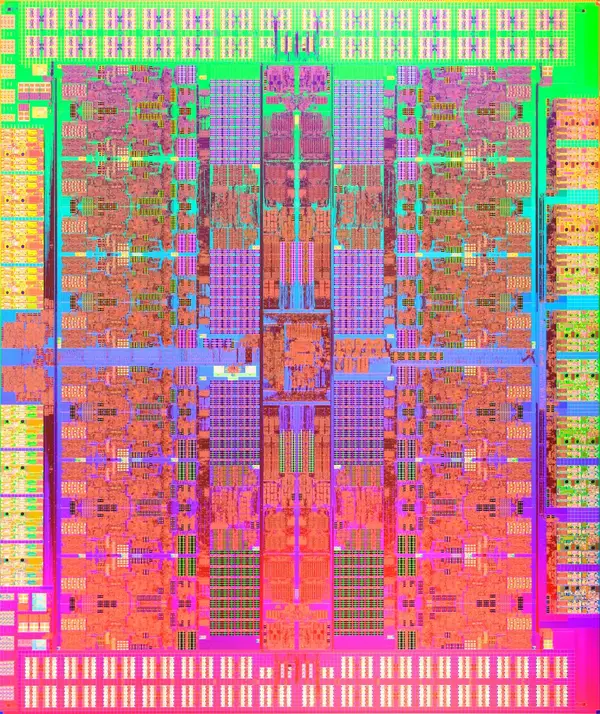

| + | == Die Shot == | ||

| + | * [[20 nn process]] | ||

| + | |||

| + | [[File:sparc64 xii die shot.png|600px]] | ||

| + | |||

| + | |||

| + | [[File:sparc64 xii die shot (annotated).png|600px]] | ||

Revision as of 22:22, 12 April 2017

Template:mpu SPARC64 XII is a high-performance 64-bit dodeca-core SPARC microprocessor designed by Fujitsu and introduced in April 2017.

Cache

| This section is empty; you can help add the missing info by editing this page. |

Expansions

| This section is empty; you can help add the missing info by editing this page. |

Die Shot

Hidden category: