From WikiChip

Difference between revisions of "loongson/godson 2/2e"

| Line 86: | Line 86: | ||

| socket 0 type = | | socket 0 type = | ||

}} | }} | ||

| − | '''Godson-2E''' ('''龙芯2E''') is a {{arch|64}} [[MIPS]] performance processor developed by [[Institute of Computing Technology of the Chinese Academy of Sciences|ICT]] and later [[Loongson]] for desktop computers. Introduced in early [[2006]], the Godson-2E operates at up to 1 GHz consuming 7W. This chip was manufactured on [[STMicroelectronics]]' [[90 nm process]] and provides roughly three times the performance of {{\\|2C}} | + | '''Godson-2E''' ('''龙芯2E''') is a {{arch|64}} [[MIPS]] performance processor developed by [[Institute of Computing Technology of the Chinese Academy of Sciences|ICT]] and later [[Loongson]] for desktop computers. Introduced in early [[2006]], the Godson-2E operates at up to 1 GHz consuming 7W. This chip was manufactured on [[STMicroelectronics]]' [[90 nm process]] and provides roughly three times the performance of {{\\|2C}}. |

The Godson-2E introduces a number of improvements over {{\\|2C|its predecessor}}, including double the clock frequency, the addition of a large [[L2 cache]], and the integration of the [[northbridge]] on-die, supporting up to DDR-333. | The Godson-2E introduces a number of improvements over {{\\|2C|its predecessor}}, including double the clock frequency, the addition of a large [[L2 cache]], and the integration of the [[northbridge]] on-die, supporting up to DDR-333. | ||

Revision as of 20:41, 19 March 2017

Template:mpu Godson-2E (龙芯2E) is a 64-bit MIPS performance processor developed by ICT and later Loongson for desktop computers. Introduced in early 2006, the Godson-2E operates at up to 1 GHz consuming 7W. This chip was manufactured on STMicroelectronics' 90 nm process and provides roughly three times the performance of 2C.

The Godson-2E introduces a number of improvements over its predecessor, including double the clock frequency, the addition of a large L2 cache, and the integration of the northbridge on-die, supporting up to DDR-333.

Cache

- Main article: GS464 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Graphics

This chip had no integrated graphics processing unit.

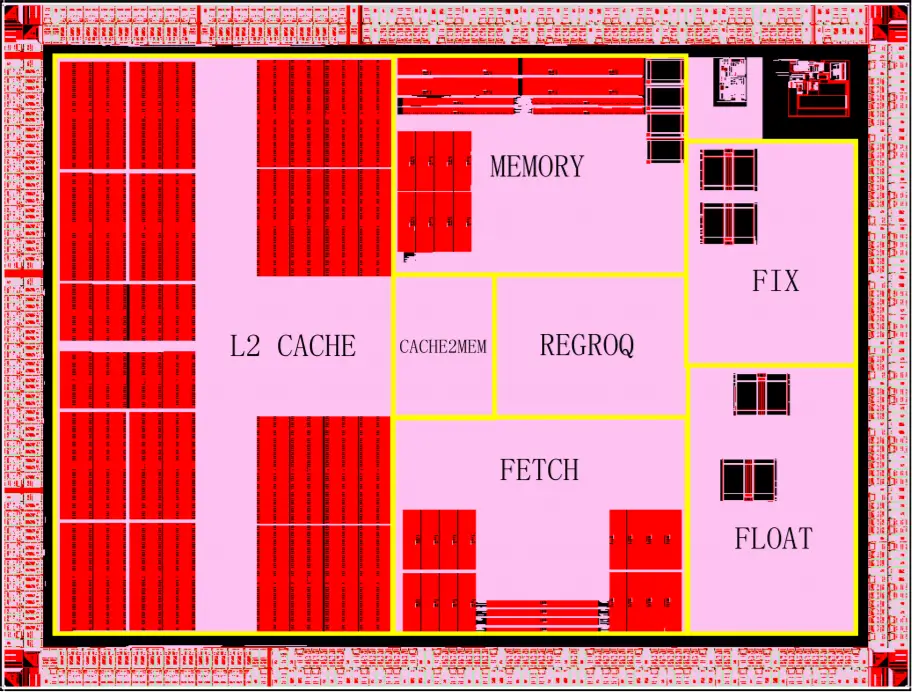

Die Shot

- 90 nm process

- 47,000,000 transistors

- 36 mm²

References

- Hu, Wei-Wu, and Jian Wang. "Making effective decisions in computer architects’ real-world: Lessons and experiences with Godson-2 processor designs." Journal of Computer Science and Technology 23.4 (2008): 620-632.

Facts about "Godson-2E - Loongson"

| has ecc memory support | true + |

| l1$ size | 128 KiB (131,072 B, 0.125 MiB) + |

| l1d$ description | 4-way set associative + |

| l1d$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l2$ description | 4-way set associative + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| max memory bandwidth | 4.967 GiB/s (5,086.208 MiB/s, 5.333 GB/s, 5,333.276 MB/s, 0.00485 TiB/s, 0.00533 TB/s) + |

| max memory channels | 1 + |

| supported memory type | DDR-333 + |