From WikiChip

Difference between revisions of "acorn/microarchitectures/arm1"

| Line 1: | Line 1: | ||

{{armh title|ARM1|arch}} | {{armh title|ARM1|arch}} | ||

| + | {{microarchitecture | ||

| + | | atype = CPU | ||

| + | | name = ARM1 | ||

| + | | designer = ARM Holdings | ||

| + | | manufacturer = VLSI Technology | ||

| + | | introduction = 1985 | ||

| + | | phase-out = | ||

| + | | process = 3 µm | ||

| + | | cores = 1 | ||

| + | |||

| + | | pipeline = <!-- yes for following options --> | ||

| + | | type = <!-- e.g. "Superscalar" --> | ||

| + | | type 2 = | ||

| + | | type N = | ||

| + | | OoOE = <!-- Yes or No only --> | ||

| + | | speculative = <!-- Yes or No only --> | ||

| + | | renaming = <!-- Yes or No only --> | ||

| + | | stages = <!-- ONLY IF FIXED SIZE, otherwise use below for range --> | ||

| + | | stages min = | ||

| + | | stages max = | ||

| + | | issues = | ||

| + | |||

| + | | inst = Yes | ||

| + | | isa = ARMv1 | ||

| + | | feature = | ||

| + | | extension = | ||

| + | |||

| + | | cache = Yes | ||

| + | | l1i = 0 KiB | ||

| + | | l1i per = Core | ||

| + | | l1i desc = | ||

| + | | l1d = 0 KiB | ||

| + | | l1d per = Core | ||

| + | | l1d desc = | ||

| + | | l2 = | ||

| + | | l2 per = | ||

| + | | l2 desc = | ||

| + | | l3 = | ||

| + | | l3 per = | ||

| + | | l3 desc = | ||

| + | |||

| + | | succession = Yes | ||

| + | | predecessor = | ||

| + | | predecessor link = | ||

| + | | successor = ARM2 | ||

| + | | successor link = arm holdings/microarchitectures/arm2 | ||

| + | }} | ||

'''ARM1''' was the first [[ARM]] microarchitecture implemented by [[ARM Holdings]] (then [[Acorn Computers]]) as a research and development project for the BBC Computer Literacy Project. ARM1 was introduced in [[1985]] and was extended to be used as a [[coprocessor]] in the Acorn's [[BBC Micro]] microcomputers. ARM1 was distributed as an evaluation system and was never commercialized. | '''ARM1''' was the first [[ARM]] microarchitecture implemented by [[ARM Holdings]] (then [[Acorn Computers]]) as a research and development project for the BBC Computer Literacy Project. ARM1 was introduced in [[1985]] and was extended to be used as a [[coprocessor]] in the Acorn's [[BBC Micro]] microcomputers. ARM1 was distributed as an evaluation system and was never commercialized. | ||

| − | == | + | == History == |

{{main|arm/history|l1=ARM's History}} | {{main|arm/history|l1=ARM's History}} | ||

| − | The '''ARM1''' is Acorn Computers first microprocessor design | + | The '''ARM1''' is Acorn Computers first microprocessor design. The ARM1 was the initial result of the ''Advanced Research and Development'' division Acorn Computers formed in order to advance the development of their own [[RISC]] processor. At the time the ARM1 was the simplest RISC processor produced. |

| + | |||

| + | == Architecture == | ||

| + | === Overview === | ||

| + | * Fabrication | ||

| + | ** [[VLSI Technology]] | ||

| + | ** [[3 µm process]] | ||

| + | ** 24,800 [[transistors]] | ||

| + | ** 50 mm² | ||

| + | |||

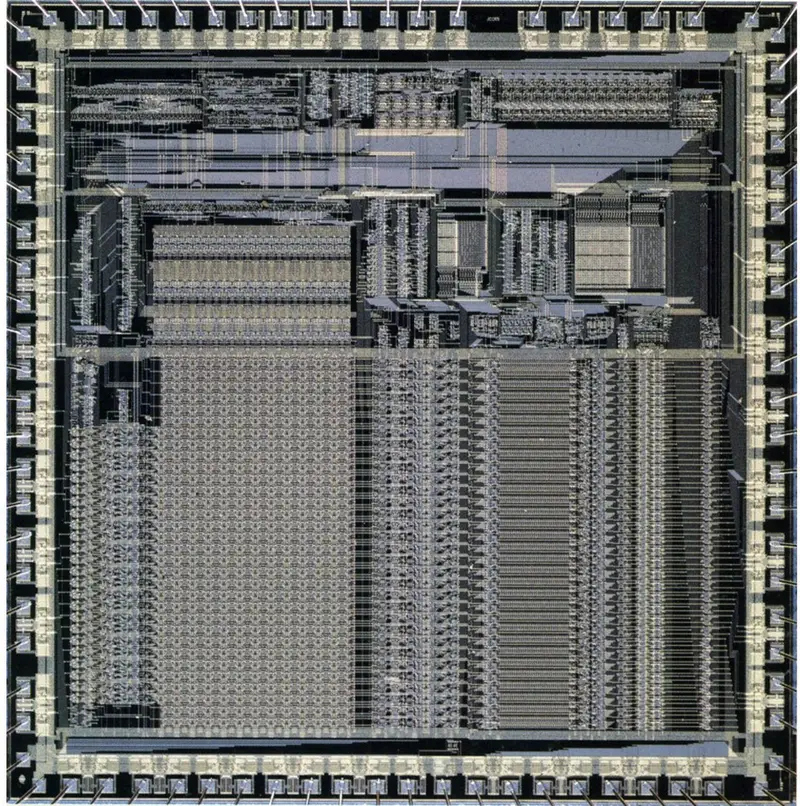

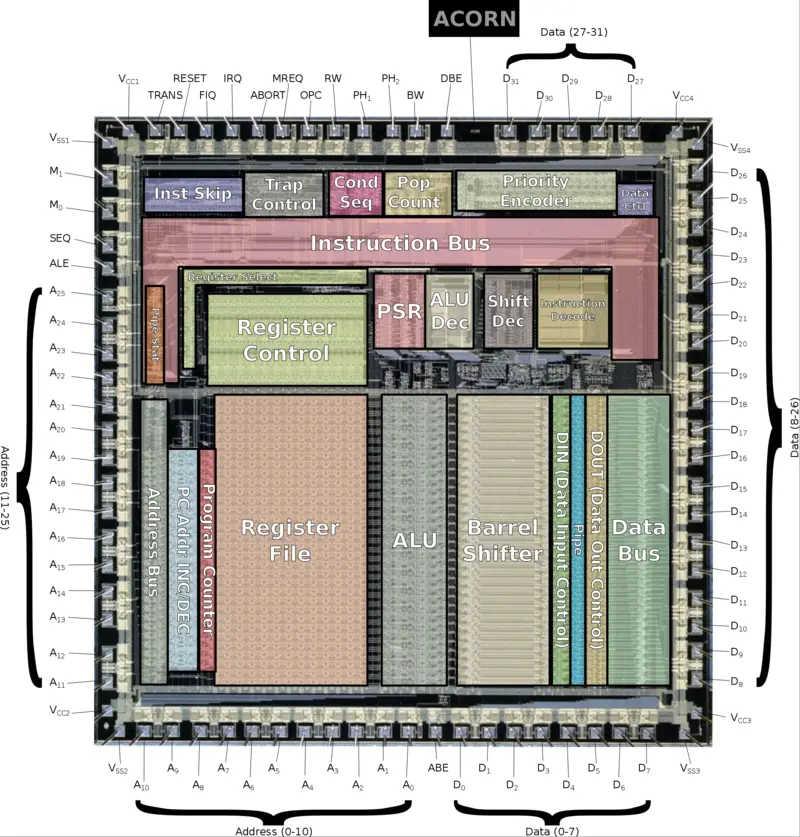

| + | == Die Shot == | ||

| + | [[File:arm1 die shot.png|800px]] | ||

| + | |||

| + | |||

| + | [[File:arm1 die shot (annotated).png|800px]] | ||

Revision as of 18:11, 12 February 2017

| Edit Values | |

| ARM1 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | ARM Holdings |

| Manufacturer | VLSI Technology |

| Introduction | 1985 |

| Process | 3 µm |

| Core Configs | 1 |

| Instructions | |

| ISA | ARMv1 |

| Cache | |

| L1I Cache | 0 KiB/Core |

| L1D Cache | 0 KiB/Core |

| Succession | |

ARM1 was the first ARM microarchitecture implemented by ARM Holdings (then Acorn Computers) as a research and development project for the BBC Computer Literacy Project. ARM1 was introduced in 1985 and was extended to be used as a coprocessor in the Acorn's BBC Micro microcomputers. ARM1 was distributed as an evaluation system and was never commercialized.

Contents

History

- Main article: ARM's History

The ARM1 is Acorn Computers first microprocessor design. The ARM1 was the initial result of the Advanced Research and Development division Acorn Computers formed in order to advance the development of their own RISC processor. At the time the ARM1 was the simplest RISC processor produced.

Architecture

Overview

- Fabrication

- VLSI Technology

- 3 µm process

- 24,800 transistors

- 50 mm²

Die Shot

Facts about "ARM1 - Microarchitectures - Acorn"

| codename | ARM1 + |

| core count | 1 + |

| designer | ARM Holdings + |

| first launched | 1985 + |

| full page name | acorn/microarchitectures/arm1 + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv1 + |

| manufacturer | VLSI Technology + |

| microarchitecture type | CPU + |

| name | ARM1 + |

| process | 3,000 nm (3 μm, 0.003 mm) + |