From WikiChip

Difference between revisions of "annapurna labs/graviton/graviton3"

| Line 37: | Line 37: | ||

[[File:graviton3 layout.png|thumb|left]] | [[File:graviton3 layout.png|thumb|left]] | ||

[[File:graviton3 features.png|thumb|right]] | [[File:graviton3 features.png|thumb|right]] | ||

| + | [[File:AWS Graviton3 Processor.jpg|thumb|right]] | ||

{{clear|left}} | {{clear|left}} | ||

Latest revision as of 01:58, 12 December 2023

| Edit Values | |

| AWS Graviton3 | |

| |

| Graviton3 Package Front | |

| |

| General Info | |

| Designer | Annapurna Labs |

| Manufacturer | TSMC |

| Market | Server |

| Introduction | November 30, 2021 (announced) November 30, 2021 (launched) |

| General Specs | |

| Family | Graviton |

| Frequency | 2,600 MHz |

| Microarchitecture | |

| ISA | ARMv8.4-A (ARM) |

| Microarchitecture | Neoverse V1 |

| Process | 5 nm |

| Transistors | 55,000,000,000 |

| Technology | CMOS |

| MCP | Yes (7 dies) |

| Word Size | 64 bit |

| Cores | 64 |

| Threads | 64 |

| Succession | |

| Contemporary | |

| Graviton3E | |

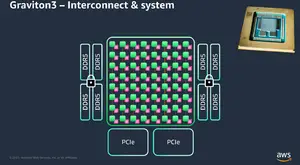

AWS Graviton3 is a tetrahexaconta-core ARMv8 microprocessor designed by Amazon (Annapurna Labs) for Amazon's own infrastructure. Graviton3 is a 5 nm 7-chiplet design SoC based on the Arm CMN-650 mesh interconnect and Neoverse V1 core microarchitecture. This chip supports octa-channel DDR5-4800 ECC memory along with 32 lanes of PCIe 5.0.

Overview[edit]

This 3rd-generation server processor was first announced during Amazon's AWS re:Invent 2021. The general rollout for the Graviton3 chip in the AWS data center occurred in early 2022. These processors are offered as part of Amazon's EC2 instances.

Cache[edit]

- Main article: Neoverse V1 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||

|

||||||||||||

Expansions[edit]

|

Expansion Options

|

||||||||

|

||||||||

Raw info[edit]

lscpu[edit]

# lscpu Architecture: aarch64 CPU op-mode(s): 32-bit, 64-bit Byte Order: Little Endian CPU(s): 1 On-line CPU(s) list: 0 Vendor ID: ARM Model: 1 Thread(s) per core: 1 Core(s) per socket: 1 Socket(s): 1 Stepping: r1p1 BogoMIPS: 2100.00 Flags: fp asimd evtstrm aes pmull sha1 sha2 crc32 atomics fphp asimdhp cpuid asimdrdm jscvt fcma lrcpc dcpop sha3 sm3 sm4 asimddp sha512 sve asimdfhm dit uscat ilrcpc flagm ssbs paca pacg dcpodp sve i8mm svebf16 i8mm bf16 dgh rng L1d: 64 KiB L1i: 64 KiB L2: 1 MiB L3: 32 MiB NUMA node(s): 1 NUMA node0 CPU(s): 0

See ARMv8 features for a description of flags.

Facts about "AWS Graviton3 - Annapurna Labs (Amazon)"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | AWS Graviton3 - Annapurna Labs (Amazon)#io + |

| base frequency | 2,600 MHz (2.6 GHz, 2,600,000 kHz) + |

| core count | 64 + |

| designer | Annapurna Labs + |

| die count | 7 + |

| family | Graviton + |

| first announced | November 30, 2021 + |

| first launched | November 30, 2021 + |

| full page name | annapurna labs/graviton/graviton3 + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| is multi-chip package | true + |

| isa | ARMv8.4-A + |

| isa family | ARM + |

| l1$ size | 8,192 KiB (8,388,608 B, 8 MiB) + |

| l1d$ size | 4,096 KiB (4,194,304 B, 4 MiB) + |

| l1i$ size | 4,096 KiB (4,194,304 B, 4 MiB) + |

| l2$ size | 64 MiB (65,536 KiB, 67,108,864 B, 0.0625 GiB) + |

| l3$ size | 32 MiB (32,768 KiB, 33,554,432 B, 0.0313 GiB) + |

| ldate | November 30, 2021 + |

| main image |  + + |

| main image caption | Graviton3 Package Front + |

| manufacturer | TSMC + |

| market segment | Server + |

| max memory bandwidth | 286.102 GiB/s (292,968.75 MiB/s, 307.2 GB/s, 307,200 MB/s, 0.279 TiB/s, 0.307 TB/s) + |

| max memory channels | 8 + |

| max pcie lanes | 32 + |

| microarchitecture | Neoverse V1 + |

| name | AWS Graviton3 + |

| process | 5 nm (0.005 μm, 5.0e-6 mm) + |

| supported memory type | DDR5-4800 + |

| technology | CMOS + |

| thread count | 64 + |

| transistor count | 55,000,000,000 + |

| word size | 64 bit (8 octets, 16 nibbles) + |