From WikiChip

Difference between revisions of "nvidia/microarchitectures/carmel"

(→Performance claims) |

|||

| Line 54: | Line 54: | ||

{| class="wikitable" | {| class="wikitable" | ||

|- | |- | ||

| − | ! SPECint 2000 !! SPECint 2006 | + | ! SPECint 2000 Rate !! SPECint 2006 Rate |

|- | |- | ||

| 2700 || 21 | | 2700 || 21 | ||

Revision as of 21:02, 31 August 2018

| Edit Values | |

| Carmel µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Nvidia |

| Manufacturer | TSMC |

| Introduction | January 7, 2018 |

| Process | 12 nm |

| Core Configs | 8 |

| Pipeline | |

| Type | Superscalar |

| Instructions | |

| ISA | ARMv8 |

| Cache | |

| L2 Cache | 2 MiB/cluster |

| L3 Cache | 4 MiB/complex |

| Succession | |

Carmel is a the successor to Denver 2, an ARM microarchitecture for Nvidia's Tegra series of SoCs.

Contents

Process Technology

Carmel is integrated into chips fabricated on TSMC 12 nm process (12FFN)

Architecture

Nvidia disclosed very few details regarding Carmel. Carmel is a 10-wide superscalar with each core supporting dual execution mode.

Key changes from Denver 2

- 12 nm (12FFN)

- ARMv8.2

- ARM RAS standard support

- Wider dispatch (10, up from 7)

Memory Hierarchy

- Cache

- Parity & ECC

- L1

- L2

- 2 MiB

- Shared per duplex

- 2 MiB

- L3

- 4 MiB

- Shared by entire cluster

- Exclusive

- 4 MiB

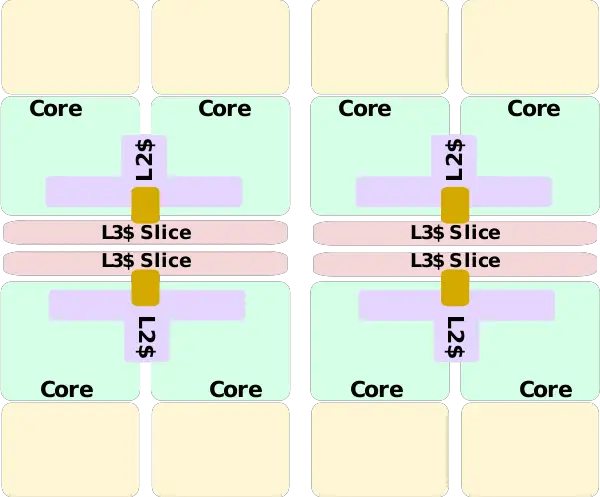

Block Diagram

CPU Complex

Overview

Carmel is a CPU microarchitecture designed by Nvidia for their SoCs. The design consists of an 8-core cluster made of 4 core duplexes. The entire complex has cache coherency as well as an I/O coherent memory subsystem which is designed for communication with the various other accelerators on their SoCs such as the vision accelerator, deep learning accelerator, multimedia engine, and the GPU.

Performance claims

| SPECint 2000 Rate | SPECint 2006 Rate |

|---|---|

| 2700 | 21 |

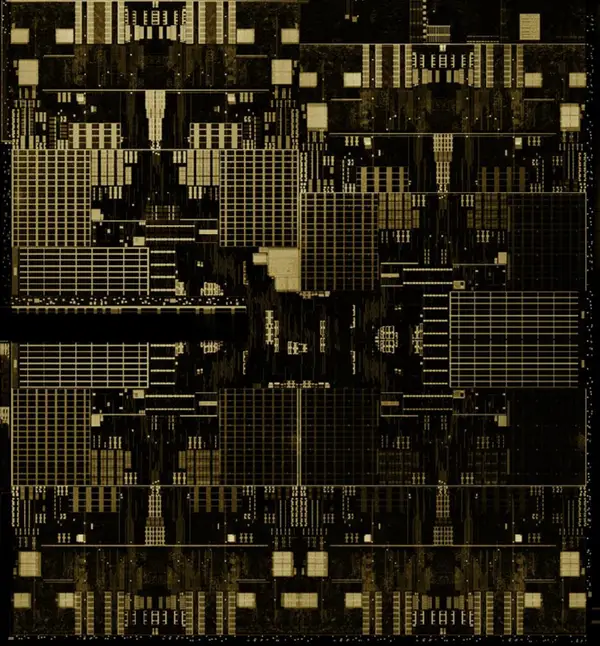

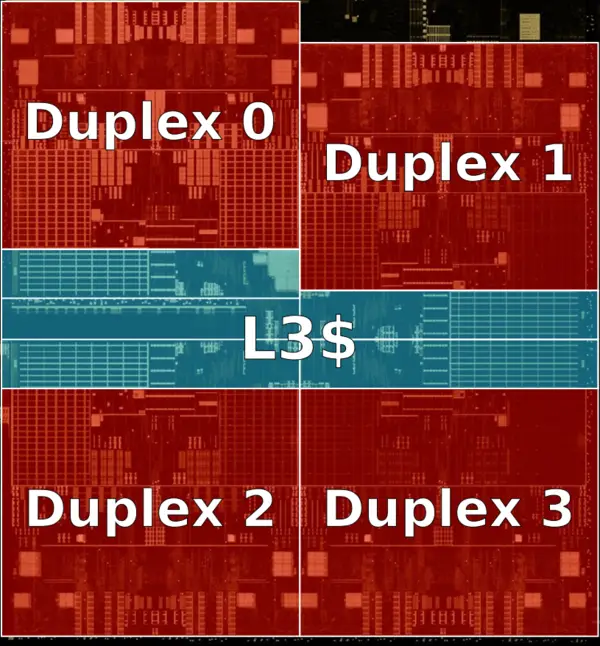

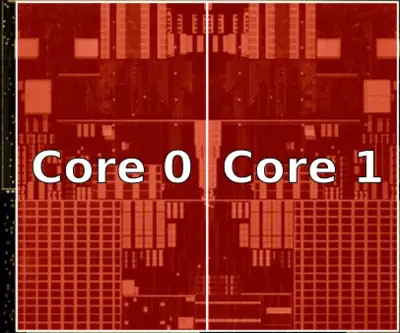

Die

CPU Complex

- 8 cores

- 4 duplexes

- shared L3

- ~62.25 mm² die size area

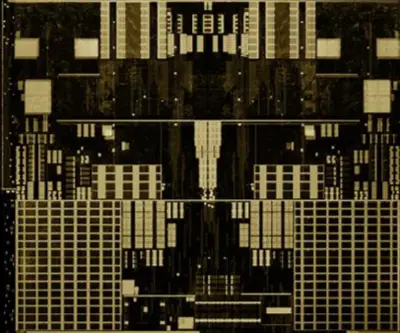

CPU Duplex

- 2 cores

- ~11.4 mm² die size area

Core

- ~5.75 mm² die size area

Bibliography

- IEEE Hot Chips 30 Symposium (HCS) 2018.

Facts about "Carmel - Microarchitectures - Nvidia"

| codename | Carmel + |

| core count | 8 + |

| designer | Nvidia + |

| first launched | January 7, 2018 + |

| full page name | nvidia/microarchitectures/carmel + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Carmel + |

| process | 12 nm (0.012 μm, 1.2e-5 mm) + |