From WikiChip

Difference between revisions of "ampere computing/emag/8180"

| Line 29: | Line 29: | ||

}} | }} | ||

'''A1''' is a {{arch|64}} [[32-core]] [[ARM]] server microprocessor introduced by [[ampere computing|Ampere]] in [[2018]]. Fabricated on [[TSMC]]'s [[16 nm process|16FF+]], this processor operates at ? with a turbo frequency of up to 3.3 GHz and 125 W TDP. This processor supports up to 8 channels of DDR4-2666 ECC memory. | '''A1''' is a {{arch|64}} [[32-core]] [[ARM]] server microprocessor introduced by [[ampere computing|Ampere]] in [[2018]]. Fabricated on [[TSMC]]'s [[16 nm process|16FF+]], this processor operates at ? with a turbo frequency of up to 3.3 GHz and 125 W TDP. This processor supports up to 8 channels of DDR4-2666 ECC memory. | ||

| + | |||

| + | {{unknown features}} | ||

| + | |||

| + | |||

| + | == Cache ==<!-- | ||

| + | {{main|ampere_computing/microarchitectures/????????#Memory_Hierarchy|l1=???? § Cache}}--> | ||

| + | {{cache size | ||

| + | |l1 cache=2 MiB | ||

| + | |l1i cache=1 MiB | ||

| + | |l1i break=32x32 KiB | ||

| + | |l1d cache=1 MiB | ||

| + | |l1d break=32x32 KiB | ||

| + | |l1d policy=write-through | ||

| + | |l2 cache=4 MiB | ||

| + | |l2 break=16x256 KiB | ||

| + | |l3 cache=32 MiB | ||

| + | |l3 break=1x32 MiB | ||

| + | }} | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=DDR4-2666 | ||

| + | |type 2=DDR4-2400 | ||

| + | |ecc=Yes | ||

| + | |max mem=1 TiB | ||

| + | |controllers=8 | ||

| + | |channels=8 | ||

| + | |max bandwidth=158.95 GiB/s | ||

| + | |bandwidth schan=19.89 GiB/s | ||

| + | |bandwidth dchan=39.72 GiB/s | ||

| + | |bandwidth qchan=79.47 GiB/s | ||

| + | |bandwidth ochan=158.95 GiB/s | ||

| + | |bandwidth hchan=119.21 GiB/s | ||

| + | }} | ||

| + | |||

| + | == Expansions == | ||

| + | {{expansions main | ||

| + | | | ||

| + | {{expansions entry | ||

| + | |type=PCIe | ||

| + | |pcie revision=3.0 | ||

| + | |pcie lanes=48 | ||

| + | |pcie config=x16 | ||

| + | |pcie config 2=x8 | ||

| + | |pcie config 3=x4 | ||

| + | }} | ||

| + | }} | ||

Revision as of 02:45, 7 February 2018

a1

| Edit Values | |||||||

| A1 | |||||||

| |||||||

| General Info | |||||||

| Designer | Ampere Computing | ||||||

| Manufacturer | TSMC | ||||||

| Model Number | A1 | ||||||

| Market | Server | ||||||

| Introduction | February 5, 2018 (announced) | ||||||

| Release Price | $950 | ||||||

| General Specs | |||||||

| Turbo Frequency | 3,300 MHz | ||||||

| Microarchitecture | |||||||

| ISA | ARMv8 (ARM) | ||||||

| Process | 16 nm | ||||||

| Technology | CMOS | ||||||

| Word Size | 64 bit | ||||||

| Cores | 32 | ||||||

| Threads | 32 | ||||||

| Max Memory | 1 TiB | ||||||

| Multiprocessing | |||||||

| Max SMP | 1-Way (Uniprocessor) | ||||||

| Electrical | |||||||

| Vcore | 0.85 V | ||||||

| VI/O | 1.8, 3.3 | ||||||

| TDP | 125 W | ||||||

| Tjunction | 0 °C – 90 °C | ||||||

| Packaging | |||||||

| |||||||

A1 is a 64-bit 32-core ARM server microprocessor introduced by Ampere in 2018. Fabricated on TSMC's 16FF+, this processor operates at ? with a turbo frequency of up to 3.3 GHz and 125 W TDP. This processor supports up to 8 channels of DDR4-2666 ECC memory.

Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions

Expansion Options |

|||||

|

|||||

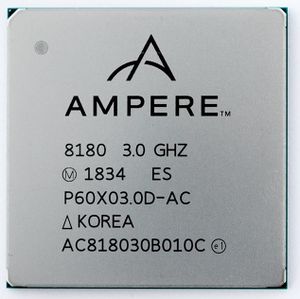

Facts about "eMAG 8180 - Ampere"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | eMAG 8180 - Ampere#package + and eMAG 8180 - Ampere#pcie + |

| base frequency | 3,000 MHz (3 GHz, 3,000,000 kHz) + |

| core count | 32 + |

| core voltage | 0.85 V (8.5 dV, 85 cV, 850 mV) + |

| designer | Ampere Computing + |

| family | eMAG + |

| first announced | February 5, 2018 + |

| first launched | September 8, 2018 + |

| full page name | ampere computing/emag/8180 + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| io voltage | 1.8 V (18 dV, 180 cV, 1,800 mV) + and 3.3 V (33 dV, 330 cV, 3,300 mV) + |

| isa | ARMv8 + |

| isa family | ARM + |

| l1$ size | 2,048 KiB (2,097,152 B, 2 MiB) + |

| l1d$ size | 1,024 KiB (1,048,576 B, 1 MiB) + |

| l1i$ size | 1,024 KiB (1,048,576 B, 1 MiB) + |

| l2$ size | 4 MiB (4,096 KiB, 4,194,304 B, 0.00391 GiB) + |

| l3$ size | 32 MiB (32,768 KiB, 33,554,432 B, 0.0313 GiB) + |

| ldate | September 8, 2018 + |

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Server + |

| max cpu count | 1 + |

| max junction temperature | 363.15 K (90 °C, 194 °F, 653.67 °R) + |

| max memory | 1,048,576 MiB (1,073,741,824 KiB, 1,099,511,627,776 B, 1,024 GiB, 1 TiB) + |

| max memory bandwidth | 158.95 GiB/s (162,764.8 MiB/s, 170.671 GB/s, 170,671.263 MB/s, 0.155 TiB/s, 0.171 TB/s) + |

| max memory channels | 8 + |

| max sata ports | 4 + |

| max usb ports | 2 + |

| microarchitecture | Skylark + |

| min junction temperature | 273.15 K (0 °C, 32 °F, 491.67 °R) + |

| model number | 8180 + |

| name | eMAG 8180 + |

| package | FCBGA-3211 + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |

| release price | $ 850.00 (€ 765.00, £ 688.50, ¥ 87,830.50) + |

| series | eMAG 1 + |

| smp max ways | 1 + |

| supported memory type | DDR4-2666 + and DDR4-2400 + |

| tdp | 125 W (125,000 mW, 0.168 hp, 0.125 kW) + |

| technology | CMOS + |

| thread count | 32 + |

| turbo frequency | 3,300 MHz (3.3 GHz, 3,300,000 kHz) + |

| word size | 64 bit (8 octets, 16 nibbles) + |