(→History) |

|||

| Line 47: | Line 47: | ||

* Chipset | * Chipset | ||

** DDR2 (from DDR) | ** DDR2 (from DDR) | ||

| + | |||

| + | == References == | ||

| + | * Intel Developer Forums, Spring 2003 | ||

Revision as of 00:30, 13 August 2017

| Edit Values | |

| Enhanced NetBurst µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Process | 90 nm, 65 nm |

| Succession | |

Enhanced NetBurst (though no actual name was given by Intel) was a planned microarchitecture designed to succeed NetBurst. On May 7 2004, Intel announced that they have cancelled the microarchitecture.

Contents

History

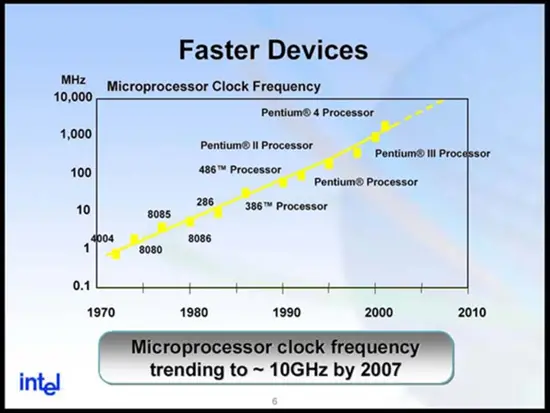

Slated to succeed NetBurst in the second half of 2004, Intel first demonstrated this microarchitecture in early 2003 with samples expected to reach partners in the second half of the year. Although no actual name was given to the microarchitecture by Intel, at least not publicly, it was expected to feature a considerably longer pipeline over Netburst and thus feature incredibly high clock rates. At IDF in 2003 Intel suggested a clock rate in excess of 5 GHz on the 90 nm process with around 8 to 9 GHz clock rate after a shrink to the 65 nm process.

On May 7, 2004 Intel announced that they've cancelled this microarchitecture and they've moved their multi-core designs forward. The likely culprit is the power wall and memory wall. During the announced Paul Otellini (then, president and chief operating officer) confirmed that "thermal considerations" were the root of the problem and that all future Intel processors will be multi-core moving forward.

Process Technology

The Enhanced NetBurst microarchitecture was planned to be manufactured initially on a 90 nm process with faster models after a process shrink to a 65 nm process.

Codenames

| Codename | Target |

|---|---|

| Tejas | Desktop microprocessors |

| Jayhawk | Server microprocessors |

Architecture

This microarchitecture was designed to deliver considerably higher clock speed by elongating the NetBurst's pipeline.

Key changes from NetBurst

- Very long pipeline

- 40-50+ stages

- Higher clock speeds

- 5 GHz+ on a 90 nm process

- 8-9 GHz+ on a 65 nm process

- New Instructions

- Tejas New Instructions (TNI) (later renamed to SSSE3)

- Chipset

- DDR2 (from DDR)

References

- Intel Developer Forums, Spring 2003

| codename | Enhanced NetBurst + |

| designer | Intel + |

| full page name | intel/microarchitectures/enhanced netburst + |

| instance of | microarchitecture + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Enhanced NetBurst + |

| process | 90 nm (0.09 μm, 9.0e-5 mm) + and 65 nm (0.065 μm, 6.5e-5 mm) + |